本帖最后由 51黑bing 于 2016-3-20 21:16 編輯

高阻態是一個數字電路里常見的術語,指的是電路的一種輸出狀態,既不是高電平也不是低電平,如果高阻態再輸入下一級電路的話,對下級電路無任何影響,和沒接一樣,如果用萬用表測的話有可能是高電平也有可能是低電平,隨它后面接的東西定(有的接在電源,有的接在地)。

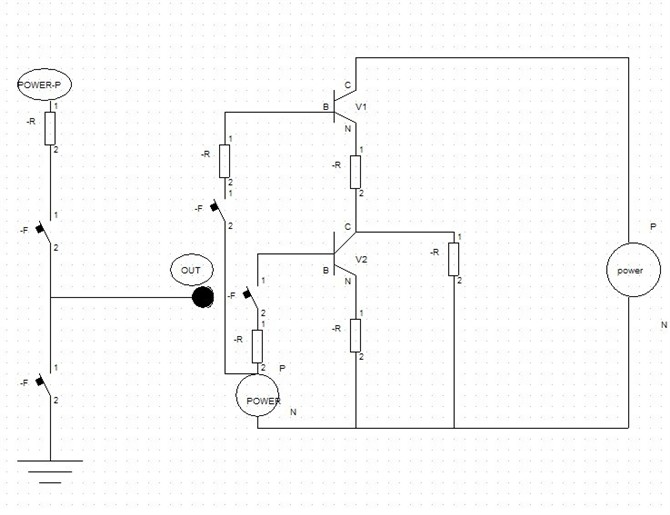

高阻態的實質:

電路分析時高阻態可做開路理解。你可以把它看作輸出(輸入)電阻非常大。他的極限可以認為懸空。也就是說理論上高阻態不是懸空,它是對地或對電源電阻極大的狀態。而實際應用上與引腳的懸空幾乎是一樣的。

高阻態的意義:

當門電路的輸出上拉管導通而下拉管截止時,輸出為高電平;反之就是低電平;如上拉管和下拉管都截止時,輸出端就相當于浮空(沒有電流流動),其電平隨外部電平高低而定,即該門電路放棄對輸出端電路的控制 。

|