���ăɂ�(g��)���͵������Լ�����(g��)�Ƕ�ȥ�����õ��c�(y��n)�C�����xֵ�c�������xֵ�ą^(q��)�e���Լ����Ե����c(di��n)��

�������xֵ�c�����xֵ����

1���������xֵ�����ԣ�

�xֵ�Z������̣�

a)Ӌ(j��)����߅�ı��_(d��)ʽ�õ��Y(ji��)��

b)���Y(ji��)���xֵ����߅��׃��

�@��(g��)�^�������S�����κ�����Verilog�Z��ĸɔ_��Ҳ�����f����Verilog�Z�䶼�������@��(g��)�r(sh��)���(zh��)�С�

2�������xֵ���ԣ�

�xֵ�Z������̣�

c)Ӌ(j��)����߅�ı��_(d��)ʽ�õ��Y(ji��)��

d)���Y(ji��)���xֵ����߅��׃��

�@��(g��)�^���в����S�Ё����κ�����Verilog�Z��ĸɔ_���@�͌�(d��o)��������Verilog�Z���(hu��)�ȴ���������ԓ�xֵ�Z���(zh��)���ꮅ����ܱ���(zh��)�У��@���������ĺ��x��

����(j��)С÷��ҕ�l��07_���������xֵ�c�������xֵ��ȥ����

һ���������xֵ����

1���������xֵԴ����

/* ��(sh��)�(y��n)���Q���������xֵ */

module mytest(clk, rst_n, a, b, c, out);

input clk, rst_n, a, b, c;

output reg [1:0] out;

reg[1:0] d;

always@(posedge clk or negedge rst_n)

if(!rst_n)

out <= 2'b0;

else begin

d <= a + b;

out <= d + c;

end

endmodule

��Դ�a�з���������(j��)�������Z�������, ���O(sh��) a = 0��b = 1, c = 0;

��(d��ng)rst_n��ߕr(sh��)������d<=a+b��out<=d+c; ��ͬ�r(sh��)��(zh��)�У����ԣ�

1������߅���_(d��)ʽ�ĽY(ji��)����a + b = 0 + 1 = 1��d + c = 0 + 0 = 0

2���ٌ��Y(ji��)���xֵ�o��߅�� d = a + 1�͵��� 1��out = d + c �͵��� 0

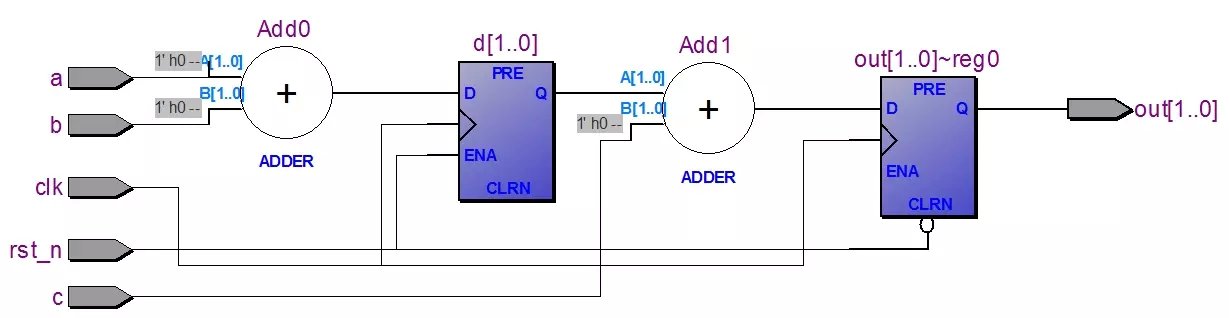

2��RTLҕ�D

�䌍(sh��)RTLҕ�D��Ҳ�ܿ����������O(sh��)a = 0��b = 1, c = 0; d�Ĵ�����0��out�Ĵ�����0 ;

��ô��(d��ng)һ��(g��)�r(sh��)����ڵ����������ɲ���(hu��)ͬ�r(sh��)��(zh��)�У���d�cout�Ĵ�����(hu��)ͬ�r(sh��)�ļӷ�����ȡֵ��

1��Add0�Ĵ�����(hu��)��a(0) + b(1) = 1��ֵ�od�Ĵ�����d�Ĵ�����0׃?y��u)?

2��Add1�Ĵ�����(hu��)��d(0) + c(0) = 0��ֵ�oout�Ĵ�����out�Ĵ�������0

3������y(c��)ԇԴ����

`timescale 1ns/1ns

`define clock_period 20

module mytest_tb;

reg clk, rst_n, a, b, c;

wire [1:0] out;

mytest u1(clk, rst_n, a, b, c, out);

initial clk = 1;

always#(`clock_period / 2) clk = ~clk;

initial begin

rst_n = 1'b0;

a = 0;

b = 0;

c = 0;

#(`clock_period * 200 + 1);

rst_n = 1'b1;

#(`clock_period * 20);

a = 0; b = 0; c = 0;

#(`clock_period * 200);

a = 0; b = 0; c = 1;

#(`clock_period * 200);

a = 0; b = 1; c = 0;

#(`clock_period * 200);

a = 0; b = 1; c = 1;

#(`clock_period * 200);

a = 1; b = 0; c = 0;

#(`clock_period * 200);

a = 1; b = 0; c = 1;

#(`clock_period * 200);

a = 1; b = 1; c = 0;

#(`clock_period * 200);

a = 1; b = 1; c = 1;

#(`clock_period * 200);

#(`clock_period * 200);

$stop;

end

endmodule

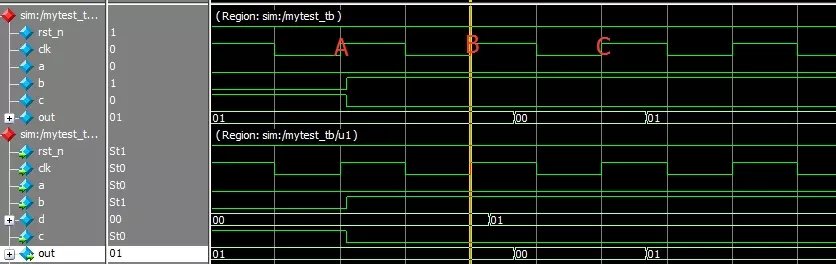

4�����ΈD

5�������

�@�� out �� 0 ׃�� 1 ǰһ��(g��)�r(sh��)����ڵ���r�����ψD���Կ�������(d��ng)�r(sh��)������أ��ɘӵõ��� a��b��d��c���ǵ���0����c���ڕr(sh��)�������֮��ű����ߣ�����Ҫ����һ��(g��)�r(sh��)����ڵ������ز��ܲɘӵ�c�Ġ�B(t��i)��

���D��

Ȼ���҂�?c��)������?span>

�����҂����� 01 �c 01 ֱ�ӊA�� 0����ô01��(du��)��(y��ng)�đ�(y��ng)ԓ�������еĜy(c��)ԇ���a���Ĵ��a���Կ�������(y��ng)ԓ��00�Ĵ��ڡ�

a = 0; b = 0; c = 1;

#(`clock_period * 200);

a = 0; b = 1; c = 0;

#(`clock_period * 200);

��?y��n)�c׃?y��u)?��b׃?y��u)?���ڕr(sh��)����ڵ�������֮���׃�����@��r(sh��)�����]���������ػ��½��ؕr(sh��)׃����

��out��d�Ġ�B(t��i)��?y��n)��^������Ҫ�ɘӺ��xֵ��������(hu��)��һ��(g��)߉���t�ĬF(xi��n)��Ҳ�����fҲ���ڕr(sh��)�������֮��ŕ�(hu��)׃������������IJ��ΈD������(j��)�ӽ���(sh��)�H��r��

���D��A�������r(sh��)�������ɲ��IJɘ�����ͬһ��(g��)�r(sh��)�������ͬ�r(sh��)�M(j��n)�У�

1��d�Ġ�B(t��i)���f��B(t��i)��0����(j��ng)�^���²����µĠ�B(t��i)��0

ͬ�r(sh��)�ɘ�a�Ġ�B(t��i)�õ���0��b�Ġ�B(t��i)�õ�����0������d�Ġ�B(t��i)׃?y��u)?

2��out�Ġ�B(t��i)���f��B(t��i)��1����(j��ng)�^���²����µĠ�B(t��i)׃?y��u)?

ͬ�r(sh��)��d��0��c�Ġ�B(t��i)�õ�����1�����Ԍ�(d��o)��out׃?y��u)?��

3���ڕr(sh��)犞鷀(w��n)���ƽ���gc׃?y��u)?��b׃?y��u)?������������֮����

��ô����B�����ؕr(sh��)�������ɲ��IJɘ�����ͬһ��(g��)�r(sh��)�������ͬ�r(sh��)�M(j��n)�У�

1��d�Ġ�B(t��i)���f��B(t��i)��0����(j��ng)�^���²����µĠ�B(t��i)��1

ͬ�r(sh��)�ɘ�a�Ġ�B(t��i)�õ���0�� b�Ġ�B(t��i)�õ�����1������d�Ġ�B(t��i)׃?y��u)?

2��out�Ġ�B(t��i)���f��B(t��i)��1����(j��ng)�^���²����µĠ�B(t��i)׃?y��u)?

ͬ�r(sh��)�ɘӵ�d��0��c�Ġ�B(t��i)�õ�����0�����Ԍ�(d��o)��out׃?y��u)?��

��(d��ng)?sh��)�C�����صĕr(sh��)�������ɲ��IJɘ�����ͬһ��(g��)�r(sh��)�������ͬ�r(sh��)�M(j��n)�У�

1��d�Ġ�B(t��i)���f��B(t��i)��1����(j��ng)�^���²����µĠ�B(t��i)��1

ͬ�r(sh��)�ɘ�a�Ġ�B(t��i)�õ���0��b�Ġ�B(t��i)�õ�����1������d�Ġ�B(t��i)׃?y��u)?

2��out�Ġ�B(t��i)���f��B(t��i)��0����(j��ng)�^���²����µĠ�B(t��i)׃?y��u)?

ͬ�r(sh��)�ɘӵ�d��1��c�Ġ�B(t��i)�õ�����0�����Ԍ�(d��o)��out׃?y��u)?��

6����Q���F(xi��n)0����r��

����ԭ��

��RTLҕ�D�п��Կ�������?y��n)���ˎׂ�(g��)d�Ĵ�����(d��o)��out�Ĵ�������һ��(g��)�r(sh��)犡�

�IJ���ҕ�D�п��Կ���Ҳ����?y��n)����d����(d��o)��out�Ĵ������F(xi��n)��0��B(t��i)��

�Y(ji��)Փ��

��dȥ�����ɣ��Ժ����^���бM����Ҫ�������g׃����������F(xi��n)����ļĴ������F(xi��n)����(d��o)�²�ͬ����

Դ�������£�

`timescale 1ns/1ns

/* ��(sh��)�(y��n)���Q���������xֵ */

module mytest(clk, rst_n, a, b, c, out);

input clk, rst_n, a, b, c;

output reg [1:0] out;

//reg[1:0] d;

always@(posedge clk or negedge rst_n)

if(!rst_n)

out <= 2'b0;

else begin

//d <= a + b;

//out <= d + c;

out <= a + b + c;

end

endmodule

RTLҕ�D�������D���Կ�������һ��(g��)�r(sh��)����ڣ���ôoutֱ�Ӿ�ȡAdd0��Add1��ֵ��

���ΈD�����D���^С�����Ԍ�(du��)������IJ��ΈD��

���������xֵ����

1��Դ�����˸������������⣬������ҕ�l���ߵ�Դ�a��

`timescale 1ns/1ns

/* ��(sh��)�(y��n)���Q���������xֵ */

module mytest(clk, rst_n, a, b, c, out);

input clk, rst_n, a, b, c;

output reg [1:0] out;

reg[1:0] d;

reg run; // �@��(g��)���Á�ָʾ��(d��ng)ǰ��(zh��)�е�λ��

always@(posedge clk or negedge rst_n)

if(!rst_n)

out = 2'b0;

else begin

d = a + b;

run =#1 1; // ��(zh��n)���(zh��)��out�xֵ�r(sh��)

out = d + c;

run =#1 0; // ��(zh��)��out�xֵ��

end

endmodule

��Դ�a�з���������(j��)�����Z�������, ���O(sh��) a = 0��b = 1, c = 0;

��(d��ng)rst_n��ߕr(sh��)������d=a+b��out=d+c; �������(zh��)�У����ԣ�

1���Ȉ�(zh��)����d = a + b = 0 + 1 = 1

2���ڈ�(zh��)�У�out = d + c = 1 + 0 = 1;

2��RTLҕ�D���]���e(cu��)���ͺ�ȥ����d�Ĵ����ķ������xֵ���a���ɵ��·һ�ӣ�

���@����ܿ����c�������xֵ�IJ�֮ͬ̎����̎���ٽ�ጡ�

3������y(c��)ԇ����

�c����������y(c��)ԇ����һ�ӣ��ԡ�

4�����ΈD

5�����ΈD����

����(j��)���a�҂�֪��run��̖(h��o)�Lj�(zh��)����d = a + b ֮�����ƽ����(zh��)���� out = d + c ����ƽ��

ͨ�^run��̖(h��o)֪����ÿ�ζ�����out׃��֮��ų��F(xi��n)���ƽ����?y��n)������ͬ�r(sh��)��(zh��)�е�Ԓ���ٶȷdz��죬����runԭ�Ⱦ��ǵ��ƽ��׃?y��u)���ƽ��׃�(y��u)���ƽ�����ӕr(sh��)1ns��Ҳ�����fͬ�r(sh��)��(zh��)��1ns֮��run��Ȼ��(hu��)�ǵ��ƽ�����D��ͬ�ӵ��ӕr(sh��)���Ğ�������ķ�ʽ��outһֱ��͡�

A�r(sh��)������ص���������������(g��)���E������(zh��)�У�

1��d�Ġ�B(t��i)����(d��ng)ǰ��B(t��i)0����(j��ng)�^�ɘӣ��µĠ�B(t��i)����0

ͬ�r(sh��)�ɘ�a�Ġ�B(t��i)��0�� b�Ġ�B(t��i)��0��d = a + b = 0 + 0 = 0;

2��run��̖(h��o)��

������

3��out�Ġ�B(t��i)����(d��ng)ǰ��B(t��i)0����(j��ng)�^�ɘӣ��µĠ�B(t��i)����0

ͬ�r(sh��)�ɘ�d�Ġ�B(t��i)0��c�Ġ�B(t��i)��0��out = d + c = 0 + 0 = 0;

4��run��̖(h��o)��

������

B�r(sh��)������ص���������������(g��)���E������(zh��)�У�

1��d�Ġ�B(t��i)����(d��ng)ǰ��B(t��i)0����(j��ng)�^�ɘӣ��µĠ�B(t��i)����0

ͬ�r(sh��)�ɘ�a�Ġ�B(t��i)��0�� b�Ġ�B(t��i)��0��d = a + b = 0 + 0 = 0;

2��run��̖(h��o)��

������

3��out�Ġ�B(t��i)����(d��ng)ǰ��B(t��i)0����(j��ng)�^�ɘӣ��µĠ�B(t��i)����1

ͬ�r(sh��)�ɘ�d�Ġ�B(t��i)0��c�Ġ�B(t��i)��1��out = d + c = 0 + 1 = 1;

4��run��̖(h��o)��

������

C�r(sh��)������ص���������������(g��)���E������(zh��)�У�

1��d�Ġ�B(t��i)����(d��ng)ǰ��B(t��i)0����(j��ng)�^�ɘӣ��µĠ�B(t��i)����0

ͬ�r(sh��)�ɘ�a�Ġ�B(t��i)��0�� b�Ġ�B(t��i)��0��d = a + b = 0 + 0 = 0;

2��run��̖(h��o)��

������

3��out�Ġ�B(t��i)����(d��ng)ǰ��B(t��i)1����(j��ng)�^�ɘӣ��µĠ�B(t��i)����1

ͬ�r(sh��)�ɘ�d�Ġ�B(t��i)0��c�Ġ�B(t��i)��1��out = d + c = 0 + 1 = 1;

4��run��̖(h��o)��

������

ͨ�^���ϲ��E���l(f��)�F(xi��n)����(zh��)�еĕr(sh��)�g���ɘӵĕr(sh��)�g��һ�ӣ���(hu��)��(d��o)�²�һ�ӵĽY(ji��)����

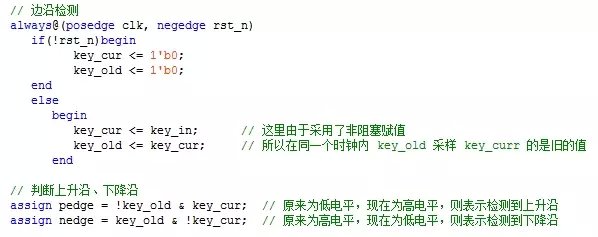

����һ��(g��)��(sh��)�(y��n)������(j��)�W(w��ng)�ϵ�һƪ���µ����ӣ�Ȼ����ͨ�^�����εķ�ʽȥ�(y��n)�C��

http://blog.163.com/xiaoting_hu/blog/static/50464772201361162838112/

һ���������xֵ����

1���������xֵ����

/* ��(sh��)�(y��n)���Q�������c�������xֵ���(sh��)�(y��n)

* �����ܣ��������xֵ - �^�� RTL-View �Լ����� */

module mytest(o_y1, o_y2, i_clk, i_rst);

output reg o_y1, o_y2;

input wire i_clk, i_rst;

//������(f��)λ alwaysA

always@(posedge i_clk or negedge i_rst)

if(!i_rst)

o_y1 <= 0; // ���ƽ��(f��)λ

else

o_y1 <= o_y2;

//������(f��)λ alwaysB

always@(posedge i_clk or negedge i_rst)

if(!i_rst)

o_y2 <= 1; // ���ƽ��(f��)λ

else

o_y2 <= o_y1;

endmodule

2��RTL ҕ�D

3������Դ����

`timescale 1ns/1ns

`define clock_period 20

module mytest_tb;

reg clk, rst;

wire y1, y2;

mytest u1(y1, y2, clk, rst);

initial clk = 1'b1;

always #(`clock_period / 2) clk = ~clk;

initial begin

rst = 1'b0; // ��(f��)λ

#(`clock_period * 5);

rst = 1'b1; // �_ʼ��(zh��)��

#(`clock_period * 20);

rst = 1'b0;

#(`clock_period * 5);

rst = 1'b1;

#(`clock_period * 20);

rst = 1'b0;

#(`clock_period * 5);

rst = 1'b1;

#(`clock_period * 20);

$stop;

end

endmodule

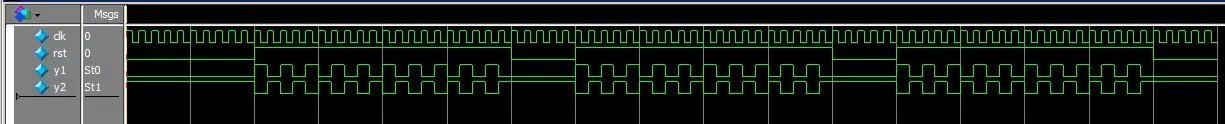

4�����ΈD

5�������

//������(f��)λ alwaysA

always@(posedge i_clk or negedge i_rst)

if(!i_rst)

o_y1 <= 0; // ���ƽ��(f��)λ

else

o_y1 <= o_y2;

//������(f��)λ alwaysB

always@(posedge i_clk or negedge i_rst)

if(!i_rst)

o_y2 <= 1; // ���ƽ��(f��)λ

else

o_y2 <= o_y1;

��(d��ng) i_rst == 0 ��o_y1 ���xֵ�� 0, o_y2 ���xֵ�� 1�����ڷ������xֵ���ԣ������o�Ⱥ����

��(d��ng) i_rst == 1 �����ڃ���(g��) always �K��(hu��)��ͬ�r(sh��)��(zh��)�С��� fpga ��(hu��)��ͬһ��(g��)�r(sh��)��������M(j��n)�вɘӣ�

��һ��(g��)�r(sh��)����ڣ�

alwaysA ��(hu��)��(du��) o_y2 �ɘӵõ�����ƽ�����Խo o_y1 �xֵ����ƽ��

alwaysB ��(hu��)��(du��) o_y1 �ɘӵõ�����ƽ�����Խo o_y2 �xֵ����ƽ��

�ڶ���(g��)�r(sh��)����ڣ�

alwaysA ��(hu��)��(du��) o_y2 �ɘӣ���?y��n)��ڵ�һ��(g��)������ o_y2 �� o_y1 ���xֵ����ƽ�����Բɘӵõ�����ƽ�����Խo o_y1 �xֵ����ƽ��

alwaysB ��(hu��)��(du��) o_y1 �ɘӣ���?y��n)��ڵ�һ��(g��)������ o_y1 �� o_y2 ���xֵ����ƽ�����Բɘӵõ�����ƽ�����Խo o_y2 �xֵ����ƽ��

֮��ĕr(sh��)����ڶ��Ǹ���(j��)�@�ӵ�Ҏ(gu��)���M(j��n)��׃���������҂������IJ��� o_y1��o_y2 ���෴��B(t��i)��

���������xֵ����

1�������xֵԴ����

/* ��(sh��)�(y��n)���Q�������c�������xֵ���(sh��)�(y��n)

* �����ܣ������xֵ - �^�� RTL-View �Լ�����

*/

module mytest(o_y1, o_y2, i_clk, i_rst);

output reg o_y1, o_y2;

input wire i_clk, i_rst;

//������(f��)λ

always@(posedge i_clk or negedge i_rst)

if(!i_rst)

o_y1 = 0; // ���ƽ��(f��)λ

else

o_y1 = o_y2;

//������(f��)λ

always@(posedge i_clk or negedge i_rst)

if(!i_rst)

o_y2 = 1; // ���ƽ��(f��)λ

else

o_y2 = o_y1;

endmodule

2��RTL ҕ�D����Ȼ������һ�ӵ� RTL ҕ�D��

3������Դ����

�ͷ���������Դ����һ�ӡ���

3�����ΈD

4�������

//������(f��)λalwaysA

always@(posedge i_clk or negedge i_rst)

if(!i_rst)

o_y1 = 0; // ���ƽ��(f��)λ

else

o_y1 = o_y2;

//������(f��)λ alwaysB

always@(posedge i_clk or negedge i_rst)

if(!i_rst)

o_y2 = 1; // ���ƽ��(f��)λ

else

o_y2 = o_y1;

��(d��ng) i_rst == 0 ��o_y1 ���xֵ�� 0, o_y2 ���xֵ�� 1, ���������xֵ���ԣ��������Ⱥ�����o���_���l���l��

��(d��ng) i_rst == 1 �����������xֵ�����ԣ��ڈ�(zh��)�������xֵ�Z��r(sh��)�����Z������ܵõ���(zh��)�С����ڃ���(g��) always �K��(hu��)��ͬ�r(sh��)��(zh��)�������� o_y1 �� o_y2 ��ȡֵ�ǻ���Ӱ푣����� o_y1��o_y2 ֵȡ�Q���ǂ�(g��) always �K���xֵ�Z���Ȉ�(zh��)�С��IJ����������@�� alwaysA ���µõ���(zh��)�С�

��һ��(g��)�r(sh��)����ڣ�

alwaysA ��(hu��)��(du��) o_y2 �ɘӵõ�����ƽ�����Խo o_y1 �xֵ����ƽ��

alwaysB ��(hu��)��(du��) o_y1 �ɘ������� alwaysA ����K o_y1 �� o_y2 ���xֵ����ƽ,���Խo o_y2 �xֵ����ƽ��

�ڶ���(g��)�r(sh��)����ڣ�

alwaysA ��(hu��)��(du��) o_y2 �ɘӣ���?y��n)��ڵ?/span>һ��(g��)������ o_y2 �� o_y1 ���xֵ�����ƽ�����Բɘӵõ������ƽ�����Խo o_y1 �xֵ�����ƽ��

alwaysB ��(hu��)��(du��) o_y1 �ɘӣ����� alwaysA ����K o_y1 �� o_y2 ���xֵ����ƽ,���Խo o_y2 �xֵ����ƽ��

Ҳ�����f o_y1 = o_y2; o_y2 = o_y1; ������(zh��)�е��������҂������IJ��� o_y1��o_y2 ���Ǹ��ƽ��B(t��i).

����Ϸ������xֵ��һ��(g��)������˼�����ӡ�

����TQQ:125739409;���g(sh��)����QQȺ281945664

����TQQ:125739409;���g(sh��)����QQȺ281945664