Tcl腳本簡介

Tcl——Tool Command Language(讀作tickle),誕生于80年代的加州大學伯克利分校,作為一種簡單高效可移植性好的腳本語言,目前已經廣泛應用在幾乎所有的EDA工具中。在Xilinx最新的FPGA設計工具Vivado中,Tcl成為唯一支持的腳本。

使用Tcl腳本的優勢如下:

- 能快速生成Vivado工程及編譯工程,生成工程所需要的PL端bit文件;生成工程之后,根據自己的需要,可手動創建Block Design,或者在腳本添加IP、實現自動連接等功能。總而言之,Tcl的引入,使得Vivado設計過程也變得可編程控制,設計流程變得更加靈活多變。

- 在開發的過程中,直接打開Vivado軟件,可視化地進行Block Design設計、配置IP和連線等。但是這樣手動添加IP或者連線需要花一定的時間,且編譯步驟重復累贅,因為打開了Vivado這個占用電腦資源比較大的軟件,導致生成需要的bitstream文件需要花費大量時間。使用腳本可以快速的在Vivado 2017.4 Tcl Shell(Vivado自帶的shell終端窗口)執行Tcl腳本命令,無需要打開Vivado軟件就進行編譯生成bit文件,花費的時間極大的縮短了。

- 如需修改工程的Block Design文件,可以打開Vivado進行修改或者直接修改Block Design Tcl腳本,所有的Block Design設計,Vivado都會自動保存成Tcl腳本文件。

基于TcL腳本生成Vivado工程

- Windows 7/10 64bit;

- Xilinx Vivado 2017.4。

表 1

由創龍提供的FPGA開發例程位于光盤Demo目錄下,本文以創龍TLK7-EVM開發板為實驗平臺,以tl-led-flash例程為例,演示使用Tcl腳本生成Vivado工程及編譯的開發步驟。 將Demo目錄下的tl-led-flash例程復制到Windows非中文路徑下,例如復制到C盤根目錄。Vivado工程目錄結構及文件說明見下表,表格中的xxx代表具體的例程,例如 tl-led-flash例程。Vivado工程的bin文件夾下存放適用于創龍各開發平臺運行的可執行文件,src文件夾下包含constraints、hdl和scripts目錄。 注意:Windows路徑有長度限制,路徑太長會導致出錯。 表 2 | | | | | | | | | | | | | | clean.sh

clear_project.tcl | |

使用TcL終端打開Tcl腳本

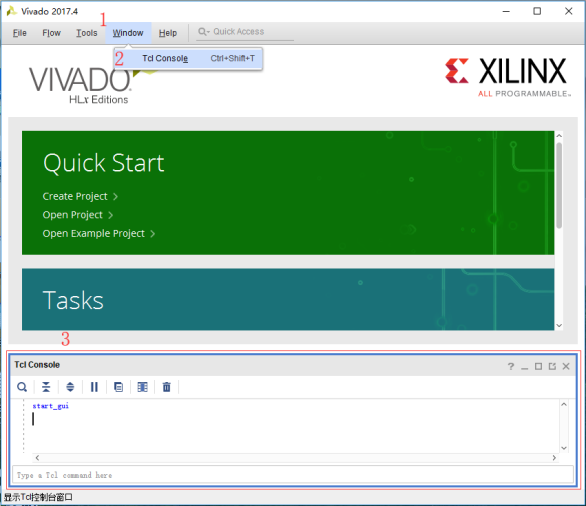

打開Vivado軟件,點擊菜單欄"Window->Tcl Consonle"打開Tcl控制臺窗口。

在Tcl控制臺窗口執行如下指令(注意指令中"/"符號的方向),進入需要執行的Tcl腳本所在路徑,該腳本文件用于生成tl-led-flash例程的Vivado工程。 Vivado% cd C:/tl-led-flash/src/scripts 生成Vivado工程

進入xxx_project.tcl腳本所在路徑,執行Tcl腳本生成對應平臺的Vivado工程。本次操作中生成創龍TLK7-EVM開發板的Vivado工程——tl_led_flash,指令參數解釋如下: Vivado%vivado -mode batch -source tl_led_flash_project.tcl -tclargs tlk7-evm xc7k325tffg676-2 - vivado -mode batch:使用vivado的batch模式;

- -source axi_gpio_project.tcl:選中要執行的Vivado工程xxx_project.tcl腳本文件;

-tclargs tlk7-evm xc7k325tffg676-2:修改"-tclargs"參數,即可生成對應開發平臺和芯片型號的工程。這里生成了TLK7-EVM開發板,FPGA型號為XC7K325TFFG676-2的Vivado工程。如需要生成TLZ7x-EasyEVM開發板,SoC芯片型號為XC7Z010CLG400-2的工程,則將指令修改為:-tclargs tlz7x-easyevm xc7z010clg400-2。 表 3 | | | | | tlz7x-easyevm xc7z010clg400-2 | | tlz7x-easyevm xc7z020clg400-2 | | | tlz7xh-evm xc7z100ffg900-2 | | | tl5728f-evm xc7a100tfgg484-2 | | | tla7-evm xc7a100tfgg484-2 | | | tlk7-evm xc7k325tffg676-2 | | | tl665xf-easyevm xc7a100tfgg484-2 | | | tl6678f-easyevm xc7k325tffg676-2 |

Tcl腳本執行完成后,Tcl控制臺窗口打印信息如下圖所示,同時在工程源碼"\src\runs"目錄下生成對應開發平臺的Vivado工程。本次生成了配套于創龍TLK7-EVM開發板的tl_led_flash工程。 Vivado工程編譯

雙擊Vivado工程"src\runs\tl_led_flash.xpr"文件  ,打開新生成的Vivado工程如下圖所示。 點擊左邊欄PROGRAM AND DEBUG下的Generate Bitsteam選項,彈出對話框中選擇Yes選項,如下圖所示: 在彈出的Launch Runs對話框中,點擊OK開始編譯Vivado工程,如下圖所示: 用時約6min后,Vivado工程編譯完成,實際編譯時間跟FPGA工程和PC性能相關。在彈出以下對話框中,點擊Cancel完成編譯步驟。 編譯完后會在Vivado工程"src\runs\xxx.runs\impl_1"目錄下生成可執行文件xxx.bit和xxx.bin,如下圖所示。其中xxx.bit文件內包含head information,可以通過下載器解析后加載到FPGA核,xxx.bin文件為可執行文件。 為便于測試,我司提供由Vivado工程編譯生成的可行文件放于bin目錄下,該目錄下包含了適用于創龍全部開發平臺的可執行文件,將其下載到開發板即可運行測試。

|