|

鎖相環的MATLAB仿真

目錄

中文摘要 3

英文摘要 4

前言 6第一章 緒論7

1.1 鎖相環的發展及國內外研究現狀7

1.2 本文的主要內容組織9

第二章 鎖相環的基本理論10

2.1鎖相環的工作原理 11

2.1.1鑒相器 11

2.1.2 低通濾波器13

2.1.3 壓控振蕩器15

2.2鎖相環的工作狀態15

2.3鎖相環的非線性工作性能分析 17

2.3.1跟蹤性能18

2.3.2捕獲性能18

2.3.3失鎖狀態19

2.4鎖相環的穩定性20

2.5信號流程圖21

2.6鎖相環的優良特性21

2.7鎖相環的應用22

2.7.1鎖相環在調制和解調中的應用22

2.7.2鎖相環在頻率合成器中的應用23

2.8本章小結23

第三章鎖相環的噪聲分析24

3.1鎖相環的輸入噪聲24

3.2壓控振蕩器的噪聲24

3.3相位噪聲的抑制26

3.4本章小結27

第四章 二階鎖相環仿真及結果28

4.1仿真介紹28

4.2程序代碼28

4.3仿真結果34

4.4本章小結36

結 論38

致謝39

參考文獻40

畢業設計小結41

摘 要 鎖相環電路是使一個特殊系統跟蹤另外一個系統,更確切的說是一種輸出信號在頻率和相位上能夠與輸入參考信號同步的電路,它是模擬及數模混合電路中的一個基本的而且是非常重要的模塊。由于鎖相環具有捕獲、跟蹤和窄帶濾波的作用,因此被應用在通信、微處理器、以及衛星等許多領域。鎖相環是通信電路里時鐘電路的一個重要模塊。 本文詳細介紹了鎖相環設計中所涉及的各項指標計。論文首先對鎖相環的發展歷史和研究現狀做了介紹,然后從其基本工作原理出發,以傳統鎖相環的結構為基礎,得到了鎖相環的數學模型,對鎖相環的跟蹤性能、捕獲性能、穩定性以及噪聲性能等各種性能進行了分析,對鎖相環的各項指標參數進行了詳細推導,得出了鎖相環數學分析的結論。本文詳細描述了鎖相環的整體電路以及鑒頻鑒相器、環路濾波器、壓控振蕩器、分頻器等電路模塊。在分析和設計的同時,也采用MATLAB軟件對電路進行了仿真。由于MATLAB仿真軟件適合多學科、多種工作平臺且功能強大、界面友好、方便快捷、語言自然并且開放性強的大型優秀應用軟件,已經也已成為國內外高等院校高等數學、數值分析、數字信號處理、自動控制理論以及工程應用等課程的基本教學工具。使用Matlab對鎖相環仿真的實現是方便快捷的。仿真結果表明,鎖相環電路達到了設計指標要求。

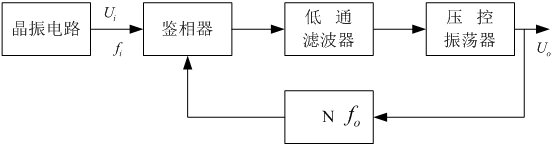

前 言 鎖相環(PLL)是一個能夠跟蹤輸入信號相位的閉環自動控制系統。它在無線電技術的各個領域得到了很廣泛的應用。最初,DeBellescize于1932年提出同步檢波理論,首次公開發表了對鎖相環路的描述,但并未引起普遍關注。直至1947年,鎖相環路才第一次應用于電視接收機水平和垂直掃描的同步。從此,鎖相環路開始得到了應用。由于技術上的復雜性以及較高的成本,應用鎖相環路的領域主要集中于航天方面,包括軌道衛星的測速定規和深空探測等。性能要求較高的精密測量儀器和通信設備有時也用到它。到70年代,隨著集成電路技術的發展,逐漸出現了集成的環路部件、通用單片集成鎖相環路以及多種專用集成鎖相環路,鎖相環逐漸變成了一個成本低、使用簡單的多功能組件,這就為鎖相技術在更廣闊的領域應用提供了條件。隨著數字技術的發展,相應出現了各種數字鎖相環,它們在數字信號傳輸的載波同步、位同步、相干解調等方面發揮了重要的作用。 在鎖相環的開發、設計研究領域,目前已經探索出多種途徑。Lindsey和Chie 講述了到1981年他們在該領域出色完成的理論研究和實驗工作。不過,大量的研究都致力于通過不同的方式實現環路鑒相器的機械化,而對于環路濾波器的設計研究則較少。典型的設計方法只是簡單地實現了在模擬鎖相環中應用廣泛的離散式環路濾波器。這種方法存在缺陷,因為在設計過程中沒有考慮到在任何采樣數據系統中都固有的計算延遲。這些延遲會使環路帶寬比根據連續時間方程計算出的結果更寬,指定帶寬和動態下的穩態相位誤差也會更大,進而降低整個環路的穩定性。 長久以來,鎖相環一直是相位相干通信系統的基石。模擬鎖相環一直占據著統治地位。隨著微電子學領域的快速發展,具備巨大優勢的數字化系統開始取代相應的模擬系統。目前的趨勢是用數字化方式設計和實現鎖相環。 第一章 緒 論 1.1 鎖相環的發展及國內外研究現狀 鎖相環(PLL-Phase Locked L00P)是自動頻率控制和自動相位控制技術的融合。人們對鎖相環的最早研究始于20世紀30年代,其在數學理論方面的原理,30年代無線電技術發展的初期就己出現。1930年建立了同步控制理論的基礎,1932年法國工程師貝爾賽什(Bellescize)發表了鎖相環路的數學描述和同步檢波論,第一次公開發表了對鎖相環路的數學描述【1】。鎖相技術首先被用在同步接收中,為同步檢波提供一個與輸入信號載波同頻的本地參考信號,同步檢波能夠在低信噪比條件下工作,且沒有大信號檢波時導致失真的缺點,因而受到人們的關注,但由于電路構成復雜以及成本高等原因,當時沒有獲得廣泛應用。 到了1943年鎖相環路第一次應用于黑白電視接收機水平同步電路中,它可以抑制外部噪聲對同步信號的干擾,從而避免了由于噪聲干擾引起的掃描隨機觸發使畫面抖動的象,使熒光屏上的電視圖像穩定清。隨后,在彩色電視接收機中鎖相電路用來同步彩色脈沖串。從此,鎖相環路開始得到了應用,迅速發展。 五十年代,隨著空間技術的發展,由杰費(Jaffe)和里希廷(Rechtin)研制成功利用鎖相環路作為導彈信標的跟蹤濾波器,他們第一次發表了含有噪聲效應的鎖相環路線性理論析文章,并解決了鎖相環路最佳設計化問題【2】。空間技術的發展促進了人們對鎖相環路及其理論的進一步探討,極大地推動了鎖相技術的發展。 六十年代初,維特比(Viterbi)研究了無噪聲鎖相環路的非線性理論問題, 發表了相干通信原理的論文。最初的鎖相環都是利用分立元件搭建的,由于技術和成本方面的原因,所以當時只是用于航天、航空等軍事和精密測量等領域。集成電路技術出現后,直到1965年左右,隨著半導體技術的發展,第一塊鎖相環芯片出現之后【3】,鎖相環才作為一個低成本的多功能組件開始大量應用各種領域。最初的鎖相環是純模擬的(APLL),所有的模塊都由模擬電路組成,它大多由四象限模擬乘法器來構建環路中的鑒相器,環路濾波器為低通濾波器(由電阻R電容C組成),壓控振蕩器的結構多種多樣。由于APLL在穩定工作時,各模塊都可以認為是線性工作的,所以也稱為線性鎖相環LPLL(Linear Phase.hckedbop)。APLL對正弦特性信號的相位跟蹤非常好,它的環路特性主要由鑒相器的特性決定。其主要用于對信號的調制。 70年代,林特賽(Undsy)和查理斯(Chanes)在做了大量實驗的基礎上進行了有噪聲的一階、二階及高階PLL的非線性理論分析。隨著人們對鎖相技術的理論和應用進行的深入廣泛的研究,伴隨著數字電路的發展,鑒相器部分開始由數字電路代替,其它部分仍為模擬電路,這種鎖相環就是最初的數字鎖相環(DPLL),準確的名稱為數模混合鎖相環(Mixed-single PLL)。隨著數模混合鎖相環技術和理的不斷發展和完善,其成為了鎖相環的主流。 現在隨著通信行中對低成本、低功耗、大帶寬、高數據傳輸速率的需求, 集成電路不斷朝著高集成度、低功耗的方向發展【4】。低功耗、高工作頻率、低電壓的鎖相環設計中,主要的挑戰是設計合適的壓控振蕩器和高頻率的分頻器,針對這方面的研究,設計師們不斷提出不同的技術,如壓控振蕩器和分頻器由原來的串接改為堆疊結構、DH-PLL結構等,隨著設計人員的不斷努力,鎖相壞的性能不斷提高,現在已經有工作頻率達50GHz的鎖相環,同時也在通信和航空航天等領域中發揮著越來越重要的作要。 國外自第一個鎖相環集成產品問世以來,幾十年問發展極為迅速,產品種類繁多,工藝日新月異。目前,除某些特殊用途的鎖相環路外,幾乎全部集成了,已生產出數百個品種。現在,鎖相技術己經成為一門系統的理論科學,它在通信、雷達、航天、精密測量、計算機、紅外、激光、原子能、立體聲、馬達控制以及圖像等技術部門獲得了廣泛的應用。 美國國家半導體(Nation Semi Conductor)于2003年6月宣布推出的LMx243x系列鎖相環芯片,其操作頻率高達3GHz以上,適用于無線局域網、5.8GHz室內無繩電話、移動電話及基站等應用方案。低功耗、超低的相位噪聲(正常化相位噪音可達到—219dBcmz)使其突顯優勢。 國內的浩凱微電子(上海)有限公司于2007年底研發出具有完全自主知識產權的高性能時鐘鎖相環IP系列產品,目前該系列產品已經過MPW硅驗證。該鎖相環系列采用全新的結構,獨特的電荷泵和差分VCO的設計,可以抑制電源和襯底噪聲對VCO的影響以確保PLL有非常低的噪聲,差分VCO的獨特設計可以輸出時鐘維持50%占空比且與VCO同頻,由于不需要倍頻振蕩,VCO本身的功耗可降為常規設計的四分之一,有效降低了功耗。相比國外而言,我國國內的IC設計水平相對比較落后,模擬設計環節更是薄弱,PLL的技術幾乎被國外壟斷,國內很少有企業掌握高性能PLL核心技術, 產品更是少。CPPLL作為應用最廣泛的一種鎖相環,雖然它的理論己經比較成熟,但是它的設計與實現涉及到信號與系統、集成電子學、版圖、半導體工藝和測試等方面,難度比較大。 1.2 本文的主要內容組織 第一章對鎖相環的發展和國內外研究現狀進行了介紹,說明了本課題研究的 重要意義。 第二章介紹了鎖相環的基本原理,介紹了鎖相環的基本構成、數學模型、工作狀態及、信號流程應用及信號流程。 第三章分析了了鎖相環噪聲的產生原因,并在數學模型上作了說明,并給出了設計建議。 第四章是二階環仿真源程序代碼及仿真結果。 第二章 鎖相環的基本理論 鎖相環作為一個系統,主要包含三個基本模塊:鑒相器(Phase Detector:PD)、低通濾波器(LowPass Filter:LPF),亦即環路濾波器(L00P Filter:LF),和壓控振蕩器(Voltage Controlled Oscillator:VCO)。這三個基本模塊組成的鎖相環為基本鎖相環,亦即線形鎖相環(LPLL),如圖2.1所示。

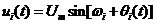

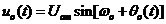

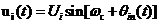

圖2.1鎖相環原理圖 當鎖相環開始工作時,輸入參考信號的頻率 與壓控振蕩器的固有振蕩頻率 與壓控振蕩器的固有振蕩頻率 總是不相同的,即 總是不相同的,即 ,這一固有頻率差 ,這一固有頻率差 必然引起它們之間的相位差不斷變化,并不斷跨越 必然引起它們之間的相位差不斷變化,并不斷跨越 角。由于鑒相器特性是以相位差 角。由于鑒相器特性是以相位差 為周期的,因此鑒相器輸出的誤差電壓總是在某一范圍內擺動。這個誤差電壓通過環路濾波器變成控制電壓加到壓控振蕩器上,使壓控振蕩器的頻率 為周期的,因此鑒相器輸出的誤差電壓總是在某一范圍內擺動。這個誤差電壓通過環路濾波器變成控制電壓加到壓控振蕩器上,使壓控振蕩器的頻率 趨向于參考信號的頻率 趨向于參考信號的頻率 ,直到壓控振蕩器的頻率變化到與輸入參考信號的頻率相等,并滿足一定條件,環路就在這個頻率上穩定下來。兩個頻率之間的相位差不隨時間變化而是一個恒定的常數,這時環路就進入“鎖定”狀態。 ,直到壓控振蕩器的頻率變化到與輸入參考信號的頻率相等,并滿足一定條件,環路就在這個頻率上穩定下來。兩個頻率之間的相位差不隨時間變化而是一個恒定的常數,這時環路就進入“鎖定”狀態。 當環路已處于鎖定狀態時,如果輸入參考信號的頻率和相位發生變化,通過環路的控制作用,壓控振蕩器的頻率和相位能不斷跟蹤輸入參考信號頻率的變化而變化,使環路重新進入鎖定狀態,這種動態過程稱為環路的“跟蹤”過程。而環路不處于鎖定和跟蹤狀態,這個動態過程稱為“失鎖”過程。 從上述分析可知,鑒相器有兩個主要功能:一個是頻率牽引,另一個是相位鎖定。實際中使用的鎖相環系統還包括放大器、分頻器、混頻器等模塊,但是這些附加的模塊不會影響鎖相環的基本工作原理,可以忽略。 2.1 鎖相環的工作原理 鎖相環作為一個系統,主要包含三個基本模塊:鑒相器【4】、低通濾波器,亦即環路濾波器,和壓控振蕩器。在本節首先分析鑒相器、環路濾波器和壓控振蕩器. 2.1.1 鑒相器 鎖相環中的鑒相器(PD)通常由模擬乘法器組成,利用模擬乘法器組成的鑒相器電路如圖示:  圖2.2 模擬鑒相器電路 鑒相器的工作原理是:設外界輸入的信號電壓和壓控振蕩器輸出的信號電壓分別為:  (2.1) (2.1)

(2.2) (2.2) 式中的 為壓控振蕩器在輸入控制電壓為零或為直流電壓時的振蕩角頻率,稱為電路的固有振蕩角頻率。則模擬乘法器的輸出電壓 為壓控振蕩器在輸入控制電壓為零或為直流電壓時的振蕩角頻率,稱為電路的固有振蕩角頻率。則模擬乘法器的輸出電壓 為: 為:

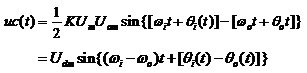

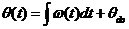

(2.3) 鑒相器的傳輸特性為:

圖2.3 鑒相器的傳輸特性 鑒相器有兩個主要功能:一個是頻率牽引,另一個是相位鎖定。實際中使用的鎖相環系統還包括放大器、分頻器、混頻器等模塊,但是這些附的模塊不會影響鎖相環的基本工作原理,可以忽略。 鑒相器的電路種類很多,大致可以分為四種常用類型: 1.乘法鑒相器。一般應用在模擬鎖相環(LPLL)中,即線性鎖相環,鑒相的范圍是[+90°,-90°]; 2.異或門鑒相器。較多應用于數字鎖相環中,鑒相范圍同為[+90°,-90°]中,要考慮鑒相器輸入的兩個信號是對稱的還是非對稱的,如是非對稱還要考慮其對PLL增益及鎖相寬度的影響; 3.JK觸發器型鑒相器。這種鑒相器由邊沿觸發,利用邊沿間的間隔進行鑒相,相位誤差為[+180°,-l80°]; 4.鑒頻鑒相器(phase—frequency detector)。其優勢就在于失鎖時,它的角頻率容易描述。這種角頻率的描述就可以實現鑒頻的功能。鑒相范圍為[+360°,-360°]。 2.1.2低通濾波器 低通濾波器(LF)的將上式2.3中的和頻分量濾掉,剩下的差頻分量作為壓控振蕩器的輸入控制電壓 。即為: 。即為:  (2.4) (2.4) 式中的 為輸入信號的瞬時振蕩角頻率, 為輸入信號的瞬時振蕩角頻率, 和 和 分別為輸入信號和輸出信號的瞬時位相,根據相量的關系可得瞬時頻率和瞬時位相的關系為: 分別為輸入信號和輸出信號的瞬時位相,根據相量的關系可得瞬時頻率和瞬時位相的關系為:

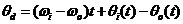

即  (2.5) 則,瞬時相位差 (2.5) 則,瞬時相位差 為 為  (2.6) (2.6)

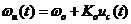

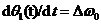

對兩邊求微分,可得頻差的關系式為:  (2.7) (2.7)

上式2.7等于零,說明鎖相環進入相位鎖定的狀態,此時輸出和輸入信號的頻率和相位保持恒定不變的狀態, 為恒定值。當上式不等于零時,說明鎖相環的相位還未鎖定,輸入信號和輸出信號的頻率不等, 為恒定值。當上式不等于零時,說明鎖相環的相位還未鎖定,輸入信號和輸出信號的頻率不等, 隨時間而變。其數學模型為: 隨時間而變。其數學模型為:

圖2.4 環路濾波器模型 環路濾波器的分類: 1.RC積分濾波器。這是結構最簡單的低通濾波器,它具有低通特性,且相位滯后。當頻率很高的時候,幅度趨于零,相位滯后接近于 ; ; 2.無源比例積分濾波器; 3.有源比例積分濾波器。它由運算放大器組成,高增益的有源比例積分濾波器又稱為理想積分濾波器。 2.1.3壓控振蕩器 壓控振蕩器(VCO)【6】的壓控特性如圖2.5所示:

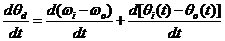

2.5壓控振蕩器特性 該特性說明壓控振蕩器的振蕩頻率 以為中心,隨輸入信號電壓 以為中心,隨輸入信號電壓 線性地變化,變化的關系如下: 線性地變化,變化的關系如下:  (2.8) (2.8) 上式說明當 隨時間而變時,壓控振蕩器(VCO)的振蕩頻率 隨時間而變時,壓控振蕩器(VCO)的振蕩頻率 也隨時間而變,鎖相環進入“頻率牽引”,自動跟蹤捕捉輸入信號的頻率,使鎖相環進入鎖定的狀態,并保持 也隨時間而變,鎖相環進入“頻率牽引”,自動跟蹤捕捉輸入信號的頻率,使鎖相環進入鎖定的狀態,并保持 的狀態不變。 的狀態不變。 2.2鎖相環的工作狀態 鎖相環有四種工作狀態,即鎖定狀態、失鎖狀態、捕獲過程和跟蹤過程【7】。 1.鎖定狀態:整個環路己經達到輸入信號相位的穩定狀態。它指輸出信號相位等于輸入信號相位或者是兩者存在一個固定的相位差,但頻率相等。在鎖定狀態時,壓控振蕩器的電壓控制信號接近平緩。 2.失鎖狀態:環路的反饋信號與鎖相環輸入信號的頻率之差不能為零的穩狀態。當環路的結構設計有問題,或者是輸入信號超出了鎖相環的應用范圍的時候都會進入失鎖狀態。這個狀態意味著壞路沒有正常工作。 3.捕獲過程:指環路由失鎖狀態進入鎖定狀態的過程。這個狀態表明環路已經開始進入正常工作,但是還沒有達到鎖定的穩態。此過程應該是一個頻率和相位誤差不斷減小的過程。 4.跟蹤過程:是指在PLL環路處于鎖定狀態時,若此時輸入信號頻率或相位因其它原因發生變化,環路能通過自動調節,來維持鎖定狀態的過程。由于輸入信號頻率或者相位的變化引起的相位誤差一般都不大,環路可視作線性系統。PLL的這四種狀態中,前兩個狀態稱為靜態,后兩個狀態稱為動態【8】。優秀的設計可以使PLL在上電后立刻進入捕獲狀態,從而快速鎖定。 一般用四個參數指標來描述PLL的系統頻帶性能: 1.同步帶:它指的是環路能保持靜態鎖定狀態的頻率范圍。當環路鎖定時,逐步增大輸入頻率,環路最終都能保持鎖定的最大輸入固有頻差。 2.失鎖帶:鎖相環路穩定工作時的動態極限。也就是說PLL在穩定工作狀態時,輸入信號的跳變要小于這個參數,PLL才能快速鎖定。若輸入信號的跳變大于該參數而小于捕獲帶,則環路還是能鎖定,但是需要較長的時間。 3.捕獲帶:只要反饋信號和輸入信號的頻差在這一范圍內,環路總會通過捕獲而再次鎖定,隨著捕獲過程的進行,反饋信號的頻率向著輸入信號頻率方向靠近,經過一段時間后,環路進入快捕帶過程,最終達到鎖定。 4.快捕帶:在此頻差范圍內,環路不需要經歷周期跳躍就可達到鎖定,實現捕獲過程。  2.6鎖相環不同帶寬捕獲示意圖【5】 2.6鎖相環不同帶寬捕獲示意圖【5】

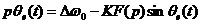

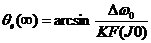

當相關頻率變化比較小時,相位誤差e大小將與頻率的變換量 成比例。而如果頻率偏移 成比例。而如果頻率偏移 達到某一特定值時,稍有變換PLL將失去捕獲相位的能力,最終失鎖。這一特定值就稱作PLL的同步帶。這個頻率范圍也稱作PLL穩定的靜態極限范圍。在失鎖時,相位誤差 達到某一特定值時,稍有變換PLL將失去捕獲相位的能力,最終失鎖。這一特定值就稱作PLL的同步帶。這個頻率范圍也稱作PLL穩定的靜態極限范圍。在失鎖時,相位誤差 將無限增加下去,同步帶內,信號的捕獲時間也是最長的。捕獲的穩定性也較差。 將無限增加下去,同步帶內,信號的捕獲時間也是最長的。捕獲的穩定性也較差。 頻率階躍信號作為輸入信號進入PLL時( 時刻頻率階躍的大小是 時刻頻率階躍的大小是 ),如果此階躍信號引起PLL的失鎖,那么就稱這個頻率階躍值為鎖出頻率值,這個范圍叫做鎖相環出鎖頻率。這個階躍信號頻差值小于PLL的同步帶。在這里,同步帶可以看作是頻率緩慢變化到此范圍使鎖相環失鎖的極值;而出鎖頻率是突然變化到此階躍值而引起PLL失鎖。而且出鎖范圍也可以理解為PLL穩定的動態范圍,在頻率階躍信號的跳變不超過出鎖范圍時PLL是滿足穩定條件的。 ),如果此階躍信號引起PLL的失鎖,那么就稱這個頻率階躍值為鎖出頻率值,這個范圍叫做鎖相環出鎖頻率。這個階躍信號頻差值小于PLL的同步帶。在這里,同步帶可以看作是頻率緩慢變化到此范圍使鎖相環失鎖的極值;而出鎖頻率是突然變化到此階躍值而引起PLL失鎖。而且出鎖范圍也可以理解為PLL穩定的動態范圍,在頻率階躍信號的跳變不超過出鎖范圍時PLL是滿足穩定條件的。 如果有一頻差值使得平均相位誤差的斜率變小,且VCO輸出的頻率值會越來越接近輸入信號的頻率,最終環路系統將重新鎖定,這一關鍵值稱作入鎖頻率。 假如輸入信號頻率與輸出信號頻率的偏移量 低于捕獲帶,則PLL將要鎖定。這個過程稱作快捕過程,它快于入鎖過程,而這個捕獲范圍也小于入鎖范圍。 低于捕獲帶,則PLL將要鎖定。這個過程稱作快捕過程,它快于入鎖過程,而這個捕獲范圍也小于入鎖范圍。 PLL捕獲的過程包含頻率捕獲與相位捕獲兩個過程,通常頻率捕獲過程所需要的時間稱為頻率捕獲時間(或頻率牽引時間);相位捕獲過程所需要的時間稱為快捕時間(或相位捕獲時間)。一般頻率捕獲時間總是大于相位捕獲時間的,所以常說的捕獲時間就是指頻率捕獲時間,不考慮相位捕獲時間的影響。 2.3鎖相環的非線性工作性能分析 當鎖相環的相位誤差大于 時,正弦鑒相器將不再能夠線性化,環路成為非線性系統,其非線性性能表現為以下三種情況:已處于鎖定狀態的鎖相環,當輸入信號頻率或壓控振蕩器自由振蕩頻率變化過大或變化速度過快時,使環路相位誤差增大到鑒相器的非線性區,這種非線性環路的性能為非線性跟蹤性能【9】;從接通到鎖定的捕獲過程中,相位誤差的變化范圍是很大的,環路處于非線性狀 時,正弦鑒相器將不再能夠線性化,環路成為非線性系統,其非線性性能表現為以下三種情況:已處于鎖定狀態的鎖相環,當輸入信號頻率或壓控振蕩器自由振蕩頻率變化過大或變化速度過快時,使環路相位誤差增大到鑒相器的非線性區,這種非線性環路的性能為非線性跟蹤性能【9】;從接通到鎖定的捕獲過程中,相位誤差的變化范圍是很大的,環路處于非線性狀 態;失鎖狀態時環路的頻率牽引現象。 2.3.1跟蹤性能 環路非線性跟蹤性能指標包括穩態相位誤差見 、同步帶 、同步帶 和最大同步掃描速 和最大同步掃描速 ,在這里從環路動態方程對其進行分析。輸入固定頻率信號的條件下,鎖相環路的動態方程可變為: ,在這里從環路動態方程對其進行分析。輸入固定頻率信號的條件下,鎖相環路的動態方程可變為:  (2.9) (2.9) 環路鎖定時瞬時相差 等于零,且鑒相器輸出誤差信號和壓控振蕩器控制信號均為直流,由此可得環路的穩態相位誤差為: 等于零,且鑒相器輸出誤差信號和壓控振蕩器控制信號均為直流,由此可得環路的穩態相位誤差為:  (2.10) (2.10)

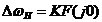

上式2.10中 為環路濾波器的直流增益。理想二階環的 為環路濾波器的直流增益。理想二階環的 ,其穩態相位誤差為: ,其穩態相位誤差為: 對于已經鎖定的環路,緩慢增加其固有頻率,環路如果還能保持鎖定,則 對于已經鎖定的環路,緩慢增加其固有頻率,環路如果還能保持鎖定,則 有解。使上式有解的環路固有頻差的最大值就是環路的同步帶,即: 有解。使上式有解的環路固有頻差的最大值就是環路的同步帶,即:  (2.11) (2.11)

則可得理想二階環路的同步帶:  (2.12) (2.12)

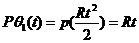

上式2.12成立的前提是環路濾波器和壓控振蕩器都有無限大的線性工作范圍,這是不符合實際的。理想二階環的同步帶是有限的,它往往受限于壓控振蕩器的最大控制范圍。理想二階環可以跟蹤頻率斜升信號,其穩態相位誤差為 。加大頻率斜升信號的斜率R,就可能使環路進入非線性跟蹤狀態。進一步加大R,環路就可能失鎖。使環路不致失鎖的尺的最大值就是最大同步掃描速率。在輸入頻率斜升信號的條件下有: 。加大頻率斜升信號的斜率R,就可能使環路進入非線性跟蹤狀態。進一步加大R,環路就可能失鎖。使環路不致失鎖的尺的最大值就是最大同步掃描速率。在輸入頻率斜升信號的條件下有:  (2.13) (2.13)

把理想二階壞的傳輸算子 代入上式2.13可得鎖定時壞路的相位誤差為: 代入上式2.13可得鎖定時壞路的相位誤差為:  (2.14) (2.14)

當 上式無解,意味著環路失鎖,因此理想二階環的最大同步掃描速率為: 上式無解,意味著環路失鎖,因此理想二階環的最大同步掃描速率為:  (2.15) (2.15)

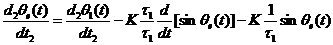

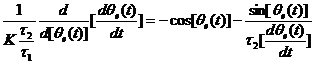

2.3.2捕獲性能 實際工作過程中,鎖相環初始狀態往往是失鎖狀態。環路經由失鎖進入鎖定狀態,需要經歷一個捕獲過程。捕獲過程分為頻率捕獲和相位捕獲兩個過程。在相位捕獲中環路相位誤差不會發生 周期跳躍,捕獲時間比較短,因此相位捕獲也叫做快捕。與相位捕獲相比,頻率捕獲時間較長,它構成了捕獲時間的主要部分。一般而言,捕獲過程中環的瞬時相差將在大范圍內變化,使捕獲過程表現為一種非線性現象。要想獲得環路捕獲性能的全部結果,需要求解環路非線性動態方程,二階環路的動態方程是二階非線性微分方程,在數學上是無法精確求解的,只能用近似求解的方法求解。理想二階環的方程為: 周期跳躍,捕獲時間比較短,因此相位捕獲也叫做快捕。與相位捕獲相比,頻率捕獲時間較長,它構成了捕獲時間的主要部分。一般而言,捕獲過程中環的瞬時相差將在大范圍內變化,使捕獲過程表現為一種非線性現象。要想獲得環路捕獲性能的全部結果,需要求解環路非線性動態方程,二階環路的動態方程是二階非線性微分方程,在數學上是無法精確求解的,只能用近似求解的方法求解。理想二階環的方程為:  (2.16) (2.16)

設環路輸入信號頻率固定,則   (2.17) (2.17) 代入并簡化,可得理想二階環軌跡方程:

(2.18) (2.18)

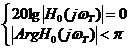

由上式可得到理想二階環的捕獲特性,如下表 2.6理想二階環的捕獲特性 實際情況中環路的捕獲帶不會為無窮大【10】,它受到壓控振蕩器最大頻率范圍的限制。 2.3.3失鎖狀態 鎖相環失鎖時,具有頻率牽引現象。當環路失鎖時,環路中誤差電壓為上下不對稱的周期性差拍信號,此差拍電壓的直流分量使壓控振蕩器的平均頻率向輸入信號頻率靠近,從而使環路輸出信號的平均頻差小于環路固有頻差。 2.4鎖相環的穩定性 鎖相環是一個負反饋系統,要工作正常,首先必須穩定,不穩定就不能實現相位的自動調節。通常的系統穩定性,是指系統在有限輸入的作用下輸出有限響應。 對于線形系統而言,其穩定性與輸入信號的大小無關,只取決于系統傳遞函數極點的位置。線形系統穩定的必要和充分條件,是系統閉環傳遞函數的所有點都具有負實部,或者說都位于s平面的左半部。 鎖相環路本質是一個非線性系統,它的穩定性是一個非線性問題。非線性系統的穩定性取決于系統本身和輸入。因此,通常把非線性系統的穩定性分為強干擾作用下和弱干擾作用下的穩定性問題,或者叫大穩定性和小穩定性問題。對于鎖相環來說,前者相當于環路失鎖而處于捕獲狀態,后者相當于同步狀態。對于大穩定性問題,主要研究環路的捕捉問題。同步狀態是環路的線形工作狀態,所以小穩定性問題實際上是一個線形系統的穩定性問題。 判斷系統穩定性的方法,通常叫巴克豪森準則【11】。對于一個反饋系統,如果其環路增益超過1,同時環路相移超過 ,即同時滿足起振的振幅條件和位條件,那么此反饋系統是不穩定的,巴克豪森準則判斷系統穩定性的條件是: ,即同時滿足起振的振幅條件和位條件,那么此反饋系統是不穩定的,巴克豪森準則判斷系統穩定性的條件是:

或  (2.19) (2.19)

公式2.19中 是增益臨界頻率,為開環增益達到0dB時的頻率。 是增益臨界頻率,為開環增益達到0dB時的頻率。 相位臨界頻率,為開環相移達到萬時的頻率。 相位臨界頻率,為開環相移達到萬時的頻率。 對于閉環不穩定的環路必有對于閉環穩定的環路,必有ωT>ωK;閉環臨界的情況為 。在工程中,閉環臨界的穩定情況實際是不穩定的,因為實際電路中總有引起各種參數變化的因素,產生附加相移,這些都會使一個臨界穩定的壞路不穩定。所以,實際使用的環路不但是穩定的而且要遠離臨界條件。這就是“相位裕度”的問題,定義為丌環增益降至OdB時開環相移量與π的差值,此概念可以說明環路穩定的程度。 。在工程中,閉環臨界的穩定情況實際是不穩定的,因為實際電路中總有引起各種參數變化的因素,產生附加相移,這些都會使一個臨界穩定的壞路不穩定。所以,實際使用的環路不但是穩定的而且要遠離臨界條件。這就是“相位裕度”的問題,定義為丌環增益降至OdB時開環相移量與π的差值,此概念可以說明環路穩定的程度。 在實際的鎖相環電路中,不可避免地存在一些寄生相移,它們引入了額外的高頻極點,不利于環路的穩定性。環路相位裕度的理論值太小,考慮到寄生相移的影響,則實際相位裕度可能更小,會使環路不穩定。 2.5信號流程圖 鎖相環的原理框圖如下:

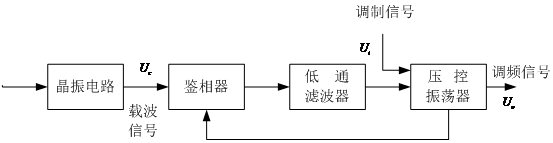

2.7鎖相環原理框圖 其工作過程如下: 1壓控振蕩器的輸出Uo經過采集并分頻; 2.輸出和基準信號同時輸入鑒相器; 3.鑒相器通過比較上述兩個信號的頻率差,然后輸出一個直流脈沖電壓Ud; 4.Ud進入到濾波器里面,濾除高頻成分后得到信息Ue; 5.Ue進入到壓控震蕩器VCO里面,控制頻率隨輸入電壓線性地變化; 6.這樣經過一個很短的時間,VCO的輸出就會穩定于某一期望值。 2.6鎖相環的優良特性 鎖相環廣泛應用于無線領域,是其自身具有較好的特性: 1.載波跟蹤特性。無論輸入鎖相環的信號是已調制好的或未調制的,只要信號中包有載波 頻率成分就可將環路設計成一個窄帶跟蹤濾波器,跟蹤輸入信號載波成分的頻率與相位變化,環路輸出信號就是需要提取(或復制)的載波信號。這就是環路的載波跟蹤特性。 載波跟蹤特性包含這三重含義:一是窄帶。環路可以有效地濾除輸入信號伴隨的噪聲和干擾。環路主要是利用環路濾波器的低通特性來實現輸入信號的載頻上的窄帶帶通特性的,這比制作普通的窄帶帶通濾波器容易得多。在高載頻上,用鎖相環路可將通帶做到幾赫茲那么窄,這是普通帶通濾波器難以實現的。二是跟蹤。環路可以在保持窄帶特性的情況下跟蹤輸入載波頻率的漂移。普通帶通濾波器的頻率特性是固定的,為了能接收載頻漂移的輸入信號,濾波器的通帶帶寬必須設計漂移范圍,因而無法利用窄帶特性來過濾噪聲與干擾。三是可將弱輸入載波信號放大到強信號輸出。因為環路輸出的是壓控振蕩器的信號,它是輸入弱載波信號頻率與相位的真實復制品,其幅度則比輸入信號強的多。 2.調制跟蹤特性。只要讓環路有適當寬度的低頻通帶,壓控振蕩器輸出信號的頻率與相位就能跟蹤輸入調頻或調相信號的頻率與相位的變化,即得到輸入角調制信號的復制品,這就是調制跟蹤特性。利用環路的調制跟蹤特性,可以制成角調制信號的調制器與解調器。 3.低門限特性。鎖相環路不像一般非線性器件那樣,門限取決于輸入信噪比,而是由環路信噪比決定的。一般環路的通頻帶總比環路輸入端的前置通頻帶窄的多,因而環路信噪比明顯高于輸入信噪比,環路能在低輸入信噪比條件下工作,即具有低門限的優良特性。這樣,只要將環路設計成窄帶,就可把淹沒在噪聲中的微弱信號提取出來。這樣的環路用于解調調頻、調相信號時,可取得門限擴展的效果;用于解調數字調制信號時,可使誤碼率降低。 2.7鎖相環的應用 2.7.1.鎖相環在調制和解調中的應用 調頻波的特點是頻率隨調制信號幅度的變化而變化。壓控振蕩器的振蕩頻率取決于輸入電壓的幅度。當載波信號的頻率與鎖相環的固有振蕩頻率 相等時,壓控振蕩器輸出信號的頻率將保持 相等時,壓控振蕩器輸出信號的頻率將保持 不變。若壓控振蕩器的輸入信號除了有鎖相環低通濾波器輸出的信號 不變。若壓控振蕩器的輸入信號除了有鎖相環低通濾波器輸出的信號 外,還有調制信號 外,還有調制信號 ,則壓控振蕩器輸出信號的頻率就是以 ,則壓控振蕩器輸出信號的頻率就是以 為中心,隨調制信號幅度的變化而變化的調頻波信號。由此可得調頻電路可利用鎖相環來組成,由鎖相環組成的調頻電路組成框圖下圖所示。 為中心,隨調制信號幅度的變化而變化的調頻波信號。由此可得調頻電路可利用鎖相環來組成,由鎖相環組成的調頻電路組成框圖下圖所示。  2.8鎖相環組成的調頻電路 2.8鎖相環組成的調頻電路

根據鎖相環的工作原理和調頻波的特點可得解調電路組成框圖如圖2.8所示。 2.7.2.鎖相環在頻率合成電路中的應用 在現代電子技術中,為了得到高精度的振蕩頻率,通常采用石英晶體振蕩器。但石英晶體振蕩器的頻率不容易改變,利用鎖相環、倍頻、分頻等頻率合成技術,可以獲得多頻率、高穩定的振蕩信號輸出。輸出信號頻率比晶振信號頻率大的稱為鎖相倍頻器電路;輸出信號頻率比晶振信號頻率小的稱為鎖相分頻器電路。鎖相倍頻和鎖相分頻電路的組成框圖下圖所示。  2.8鎖相倍頻和鎖相分頻電路 2.8鎖相倍頻和鎖相分頻電路

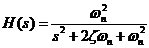

圖中的N大于1時,為分頻電路;當 時,為倍頻電路。 時,為倍頻電路。 2.8本章小結 本章對鎖相環系統的基本原理及組成部件進行了概括介紹,對鎖相環系統的捕獲、跟蹤性能,動態特性以及鎖相環的自身特性等一些基本性能、概念給出了相關說明,指出鎖相環路所以能夠得到如此廣泛的應用,是由其獨特的優良性能所決定的。它具有載波跟蹤特性,作為一個窄帶跟蹤濾波器,提取淹沒在噪聲之中的信號,在深空測控中有著廣泛的應用。 第三章鎖相環的噪聲分析 鎖相環的輸入信號和各個模塊都包括了噪聲源,其輸出信號必然包含噪聲。噪聲是鎖相環的重要特性,設計中必須考慮。本章節主要分析了輸入信號的噪聲和壓控振蕩器的噪聲。在實際的工作過程中,壓控振蕩器的相位噪聲是鎖相環最主要的噪聲。 3.1鎖相環的輸入噪聲 如下所示,以采用RC 積分濾波器的鎖相環為例。設輸入和輸出信號 積分濾波器的鎖相環為例。設輸入和輸出信號 和 和 。則由前面章節可得出傳輸函數為: 。則由前面章節可得出傳輸函數為:  (3.1) (3.1)

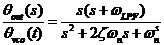

如果輸入相位偏差 不隨時間變化,即為純正弦信號。當 不隨時間變化,即為純正弦信號。當 時, 時, 。同樣,假設 。同樣,假設 變化緩慢,則上式的分母會接近 變化緩慢,則上式的分母會接近 ,所以 ,所以 仍然等于1,這表明輸出相位跟隨輸入相位,或者說是輸出頻率跟隨輸入頻率。 仍然等于1,這表明輸出相位跟隨輸入相位,或者說是輸出頻率跟隨輸入頻率。 如果 變化非常快,上式表明輸出相位偏差氣, 變化非常快,上式表明輸出相位偏差氣, 減小并最終為零,使得“ 減小并最終為零,使得“ ,即輸入相位或者頻率變化太快,鎖相環不能跟蹤輸信號。輸入信號的相位噪聲被壞路中的低通濾波器整形最后出現在輸出端。為了減小噪聲,環路帶寬應該盡量小,但這以降低鎖定范圍、限制捕獲范圍、降低穩定性為代價。 ,即輸入相位或者頻率變化太快,鎖相環不能跟蹤輸信號。輸入信號的相位噪聲被壞路中的低通濾波器整形最后出現在輸出端。為了減小噪聲,環路帶寬應該盡量小,但這以降低鎖定范圍、限制捕獲范圍、降低穩定性為代價。 3.2壓控振蕩器的噪聲 VCO的相位噪聲可以被認為是一個外加信號 ,如下圖3.1所示。在此假設, ,如下圖3.1所示。在此假設, 和 和 是不相關的。假設 是不相關的。假設 =0,即表示輸入信號的相位偏差為零,輸入信號為一個嚴格的周期信號。得到從 =0,即表示輸入信號的相位偏差為零,輸入信號為一個嚴格的周期信號。得到從 到 到 的傳遞函數: 的傳遞函數:  (3.2) (3.2)

由上所得的輸入噪聲和傳遞函數有相同的極點,但是它包括了兩個零點 和 和 ,具有高通性。 ,具有高通性。 原點上的零點表示,如果 變化緩慢,則 變化緩慢,則 很小。因為在鎖定條件下,VC0的相位變化通過PD變成了電壓,加到VCO的控制輸入端,使相位朝相反的方向變化。由于VCO的電壓相位轉變對緩慢變化的控制電壓 很小。因為在鎖定條件下,VC0的相位變化通過PD變成了電壓,加到VCO的控制輸入端,使相位朝相反的方向變化。由于VCO的電壓相位轉變對緩慢變化的控制電壓 有無窮的增益,負反饋抑制了輸出相位變化。 有無窮的增益,負反饋抑制了輸出相位變化。 PLL可以簡化為下圖結構:一個理想的積分器位于負反饋環中,在輸入端 產生了一個“虛地’,因此,對于緩慢變化的 。,則 。,則 =0。 =0。

3.1圖簡單的鎖相環VCO噪聲模擬 假設 變化很快,則 變化很快,則 的大小,以及環路增益都相應減小,這樣,也會使“虛地”產生變化。當 的大小,以及環路增益都相應減小,這樣,也會使“虛地”產生變化。當 變化接近 變化接近 ,環路增益由于低通濾波器而減小。 ,環路增益由于低通濾波器而減小。 從公式(3.2)可知,當s→∞時,有 。即 。即 當變化非常快時環路相當于開環狀態。 當變化非常快時環路相當于開環狀態。 利用壓控振蕩器傳遞函數:,將電源加一個很小的階躍q,則輸出為:  (3.3) (3.3)

由上式有時間常數為1/ 。為了使PLL有快的鎖定特性,盡量將 。為了使PLL有快的鎖定特性,盡量將 取大。 取大。 為了減小VCO的相位噪聲的影響,環路帶寬應該盡量取大,而這與抑制輸入相位噪聲將環路噪聲帶寬盡量減小相矛盾。實際工程中,輸入信號主要來自晶體振蕩器,噪聲非常小,所以,PLL的輸入相位噪聲主要來自內部的VCO,因此可以將環路帶寬適當取大。 3.3相位噪聲的抑制 鎖相環的抖動主要是由相位噪聲或邊帶引起的。而產生隨機抖動和相位噪聲的原因,可以簡單認為是電源噪聲、襯底噪聲和器件噪聲。邊帶則基本上是由控制路徑上的周期性擾動引起的。 結合實際,抖動產生的原因如有: 1.電源噪聲和襯底噪聲,引起了受電壓影響的電容(如MOS管的Cgd)的變化,導致振蕩器頻率的變化。可以把電源和襯底也作為VCO的控制電壓來分析VCO的頻率特性; 2.襯底噪聲,襯底噪聲會導致器件閾值電壓 的改變; 的改變; 3.器件噪聲(熱噪聲、閃爍噪聲),閃爍噪聲隨著振蕩器(VCO)的頻率慢慢變化,它能夠通過增加PLL的帶寬來抑制。熱噪聲可以通過版圖的方法減小。減小 噪聲要增加器件面積。 噪聲要增加器件面積。 在PLL設計過程中,應當盡量遵循以下原則來減小抖動: 1.將緩沖控制電壓(buffered control voltage)作為電源電壓。 2.用緩沖控制電壓去產生偏置電流,電流源隔離。 3.采用Cascode電流源或鏡像電流源,可以將敏感性降到O.5%。 4.用阱器件來做電流源和環路濾波電容。 5.將控制電壓做在阱上面(避免襯底的影響)。 3.4本章小結 本章對鎖相環系統噪聲進行了概括介紹,對鎖相環系統的輸入噪聲,相位噪聲給出了相關說明及減小噪聲的一些措施,指出鎖相環路設計中應該盡可能的減小噪聲帶來的影響,實際意義很重要。 第四章二階鎖相環仿真及結果 4.1仿真介紹 仿真使用的軟件是MATLAB7.0。由于MATLAB仿真軟件適合多學科、多種工作平臺且功能強大、界面友好、方便快捷、語言自然并且開放性強的大型優秀應用軟件,已經也已成為國內外高等院校高等數學、數值分析、數字信號處理、自動控制理論以及工程應用等課程的基本教學工具。使用Matlab對鎖相環仿真的實現是方便快捷的。 仿真所采有的是二階鎖相環。這是由于我們實際應用中的絕大多數PLL,或者是二階的,或者是通過忽略高階效應(至少在初步設計時)而被設計成近似的二階環路。鑒于二階鎖相環在實際應用的意義,所以在仿真采用了二階鎖相環。

- % File: c6_nltvde.m

- w2b=0; w2c=0; % initialize integrators

- yd=0; y=0; % initialize differential equation

- tfinal = 50; % simulation time

- fs = 100; % sampling frequency

- delt = 1/fs; % sampling period

- npts = 1+fs*tfinal; % number of samples simulated

- ydv = zeros(1,npts); % vector of dy/dt samples

- yv = zeros(1,npts); % vector of y(t) samples

- %

- % beginning of simulation loop

- for i=1:npts

- t = (i-1)*delt; % time

- if t<20

- ydd = 4*exp(-t/2)-3*yd*abs(y)-9*y; % de for t<20

- else

- ydd = 4*exp(-t/2)-3*yd-9*y; % de for t>=20

- end

- w1b=ydd+w2b; % first integrator - step 1

- w2b=ydd+w1b; % first integrator - step 2

- yd=w1b/(2*fs); % first integrator output

- w1c=yd+w2c; % second integrator - step 1

- w2c=yd+w1c; % second integrator - step 2

- y=w1c/(2*fs); % second integrator output

- ydv(1,i) = yd; % build dy/dt vector

- yv(1,i) = y; % build y(t) vector

- end % end of simulation loop

- plot(yv,ydv) % plot phase plane

- xlabel('y(t)') % label x axis

- ylabel('dy/dt') % label y zxis

- % End of script file.

- % File: pllpost.m

- %

- kk = 0;

- while kk == 0

- k = menu('Phase Lock Loop Postprocessor',...

- 'Input Frequency and VCO Frequency',...

- 'Input Phase and VCO Phase',...

- 'Frequency Error','Phase Error','Phase Plane Plot',...

- 'Phase Plane and Time Domain Plots','Exit Program');

- if k == 1

- plot(t,fin,'k',t,fvco,'k')

- title('Input Frequency and VCO Freqeuncy')

- xlabel('Time - Seconds');ylabel('Frequency - Hertz');pause

- elseif k ==2

- pvco=phin-phierror;plot(t,phin,t,pvco)

- title('Input Phase and VCO Phase')

- xlabel('Time - Seconds');ylabel('Phase - Radians');pause

- elseif k == 3

- plot(t,freqerror);title('Frequency Error')

- xlabel('Time - Seconds');ylabel('Frequency Error - Hertz');pause

- elseif k == 4

- plot(t,phierror);title('Phase Error')

- xlabel('Time - Seconds');ylabel('Phase Error - Radians');pause

- elseif k == 5

- ppplot

- elseif k == 6

- subplot(211);phierrn = phierror/pi;

- plot(phierrn,freqerror,'k');grid;

- title('Phase Plane Plot');xlabel('Phase Error /Pi');

- ylabel('Frequency Error - Hertz');subplot(212)

- plot(t,fin,'k',t,fvco,'k');grid

- title('Input Frequency and VCO Freqeuncy')

- xlabel('Time - Seconds');ylabel('Frequency - Hertz');subplot(111)

- elseif k == 7

- kk = 1;

- end

- end % End of script file.

- % File: pllpre.m

- %

- clear all % be safe

- disp(' ') % insert blank line

- fdel = input('Enter the size of the frequency step in Hertz > ');

- fn = input('Enter the loop natural frequency in Hertz > ');

- lambda = input('Enter lambda, the relative pole offset > ');

- disp(' ')

- disp('Accept default values:')

- disp(' zeta = 1/sqrt(2) = 0.707,')

- disp(' fs = 200*fn, and')

- disp(' tstop = 1')

- dtype = input('Enter y for yes or n for no > ','s');

- if dtype == 'y'

- zeta = 1/sqrt(2);

- fs = 200*fn;

- tstop = 1;

- else

- zeta = input('Enter zeta, the loop damping factor > ');

- fs = input('Enter the sampling frequency in Hertz > ');

- tstop = input('Enter tstop, the simulation runtime > ');

- end %

- npts = fs*tstop+1; % number of simulation points

- t = (0:(npts-1))/fs; % default time vector

- nsettle = fix(npts/10); % set nsettle time as 0.1*npts

- tsettle = nsettle/fs; % set tsettle

- % The next two lines establish the loop input frequency and phase

- % deviations.

- fin = [zeros(1,nsettle),fdel*ones(1,npts-nsettle)];

- phin = [zeros(1,nsettle),2*pi*fdel*t(1:(npts-nsettle))];

- disp(' ') % insert blank line

- % end of script file pllpre.m

- % File: pll2sin.m

- w2b=0; w2c=0; s5=0; phivco=0; %initialize

- twopi=2*pi; % define 2*pi

- twofs=2*fs; % define 2*fs

- G=2*pi*fn*(zeta+sqrt(zeta*zeta-lambda)); % set loop gain

- a=2*pi*fn/(zeta+sqrt(zeta*zeta-lambda)); % set filter parameter

- a1=a*(1-lambda); a2 = a*lambda; % define constants

- phierror = zeros(1,npts); % initialize vector

- fvco=zeros(1,npts); % initialize vector

- % beginning of simulation loop

- for i=1:npts

- s1=phin(i) - phivco; % phase error

- s2=sin(s1); % sinusoidal phase detector

- s3=G*s2;

- s4=a1*s3;

- s4a=s4-a2*s5; % loop filter integrator input

- w1b=s4a+w2b; % filter integrator (step 1)

- w2b=s4a+w1b; % filter integrator (step 2)

- s5=w1b/twofs; % generate fiter output

- s6=s3+s5; % VCO integrator input

- w1c=s6+w2c; % VCO integrator (step 1)

- w2c=s6+w1c; % VCO integrator (step 2)

- phivco=w1c/twofs; % generate VCO output

- phierror(i)=s1; % build phase error vector

- fvco(i)=s6/twopi; % build VCO input vector

- end

- % end of simulation loop

- freqerror=fin-fvco; % build frequency error vector

- % End of script file.

- function [] = pplane(x,y,nsettle)

- % Plots the phase plane with phase in the range (-pi,pi)

- ln = length(x);

- maxfreq = max(y);

- minfreq = min(y);

- close % Old figure discarded

- axis([-1 1 1.1*minfreq 1.1*maxfreq]); % Establish scale

- hold on % Collect info for new fig

- j = nsettle;

- while j < ln

- i = 1;

- while x(j) < pi & j < ln

- a(i) = x(j)/pi;

- b(i) = y(j);

- j = j+1;

- i = i+1;

- end

- plot(a,b,'k')

- a = [];

- b = [];

- x = x - 2*pi;

- end

- hold off

- title('Phase-Plane Plot')

- xlabel('Phase Error / Pi')

- ylabel('Frequency Error in Hertz')

- grid % End of script file.

- % File: ppplot.m

- % ppplot.m is the script file for plotting phase plane plots. If the

- % phase plane is constrained to (-pi,pi) ppplot.m calls pplane.m.

- kz = 0;

- while kz == 0

- k = menu('Phase Plane Options',...

- 'Extended Phase Plane',...

- 'Phase Plane mod(2pi)',...

- 'Exit Phase Plane Menu');

- if k == 1

- phierrn = phierrn/pi;

- plot(phierrn,freqerror,'k')

- title('Phase Plane Plot')

- xlabel('Phase Error /Pi')

- ylabel('Frequency Error - Hertz')

- grid

- pause

- elseif k == 2

- pplane(phierrn,freqerror,nsettle+1)

- pause

- elseif k == 3

- kz = 1;

- end end % End of script file.

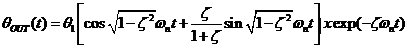

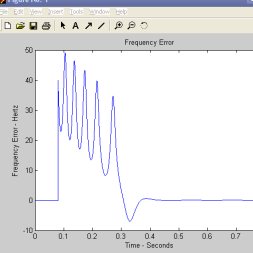

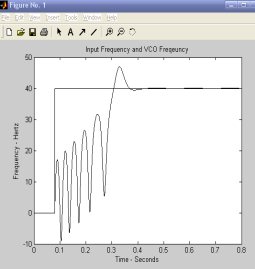

4.3仿真結果 圖4.1 鎖相環處理框 上圖是利用MATLAB提供的函數將計算結果圖形化功能建立的。在運行程序后,就會出現上面的對話框,點擊點擊其中的任何一項就會出現相應的仿真圖形。上圖中包含了輸入頻率和VCO頻率,輸入相位和VCO相位,頻率誤差,相位誤差,相位空間波特圖,相位空間和時域,退出程序等選項。 運行程序后出現如下指令: Accept the tentative values: the first loop frequency is 5 第一循環頻率 Enter y for yes or n for no > y Enter the loop gain >40 輸入環路增益為40 Enter the sampling frequency in Hertz > 1200 輸入采樣頻率 Enter tstop, the simulation runtime > 5 仿真時間為5秒 設置好參數后運行程序,由上我們可知環路增益為40,仿真時間為5s,采樣頻率為1200Hz。接著點擊上圖4.1中的菜單,就能得到如下仿真圖像。其中我們主要觀察輸入相位和VCO相位。 圖4.2 輸入相位和VCO相位 圖4.3 相位誤差圖 圖4.2中藍線為輸入相位,綠線代表VCO相位,從圖中可以看見隨著時間的變化輸入信號相位為線性,而VCO相位則是經歷了一段曲線后斜率與輸入信號相位斜率相同,輸出相位跟隨輸入相位,達到穩定。圖4.3中VCO的相位也是先經歷了一段時間的曲線后變為一條直線達到穩定。根據鎖相環的基本原理我們可知鎖相環是個反饋網絡,它是由輸出信號(VCO產生)與參考頻率在頻率和相位上保持同步或者保持常數。由此我們可以看出鎖相環工作后,在最初的一段時間中鎖相環開始工作,輸入信號經過鑒相器,環路慮波器后,將輸出相位反饋給VCO壓控振蕩器,使壓控振蕩器與輸入頻率逐步實現同步,保持一個常數,實現鎖定。其中經歷了鎖相環的失鎖、跟蹤、捕獲、鎖定,從而達到最后達到穩定狀態。從開始到達到穩定的這段時間則為做捕獲時間。   圖4.4 頻率差圖 圖4.5 輸入頻率和VCO頻率圖 圖4.4 頻率差圖 圖4.5 輸入頻率和VCO頻率圖

圖4..4與圖4.5也顯示了鎖相環工作后從失鎖、跟蹤、捕獲、鎖定的過程,過程。從不停的擺動到最后的直線狀態,這個過程稱為鎖定過程。其中我們可以發現在捕捉過程中隨著捕捉次數的增加,捕捉過程也變得較慢,這說明此時的的鎖相環工作平率處在穩定工作的動態界限內,工作正常。 4.4本章小結 本章介紹了仿真的環境以及二階鎖相環的仿真過程,并對其仿真結果進行了分析。在前三章的理論基礎上,通過使用MATLAB7.0進行了仿真。實驗結果表明:用MATLAB進行的二階鎖相環仿真達到了最初的設想,鎖相環的失鎖、跟蹤、捕獲、鎖定各個階段均有體現。達到了最初仿真的要求。 結 論 本文在閱讀一些文獻和對鎖相環有一定程度了解的基礎上,運用MATLAB進行了仿真。本文完成了以下工作: - 在掌握了鎖相環的基本原理并對文獻研究的基礎上,對鎖相環的工作原理進行了深入的分析,深入了解鎖相環技術的數學分析方法,應用此方法得到鎖相環技術的數學模型,用這些理論指導實際中的設計工作。

- 在對基本原理和電路結構確定的基礎上,將鎖相環的整體電路進行層次化分解,即鑒頻鑒相器、低通濾波器、壓控振蕩器,并對各個模塊的工作原理和性能進行了比較詳細的分析。

- 用MATLAB軟件對設計的鎖相環電路進行了模擬仿真,驗證了電路功能的正確與否,以及鎖相環的設計目標是否達到。

由于時間和條件的限制,在設計工作中有些工作沒有做到,留待進一步的完善,后續工作是: - 在運用MATLAB設計鎖相環時,并沒有引入噪聲對鎖相環的影響及相應的分析,也未對鎖相環的各項參數進行深入的討論。

- 僅限于對鎖相環理論的研究與分析上,并沒有針對其實際中的應用研究相關的了解。

- 在此次仿真中只對二階鎖相環進行了仿真,并沒有對其他鎖相環進行仿真和研究,也沒有進行硬件實現。

目前鎖相環技術在通信中早已成熟,隨著科技的發展,目前的鎖相環都是基于半導體工藝的集成電路。對于未來而言,用鎖相環的集成化設計減小相應噪聲、提高鎖相環的頻率預測精度、硬件系統的運算速率以及降低干擾也是其研究的一個重要方向。

完整的Word格式文檔51黑下載地址:

鎖相環與MATLAB仿真.doc

(508 KB, 下載次數: 50)

鎖相環與MATLAB仿真.doc

(508 KB, 下載次數: 50)

2018-5-31 10:25 上傳

點擊文件名下載附件

下載積分: 黑幣 -5

|