這是我用Altera公司下集成軟件Quartus II硬件開發板來實現的,通過Verilog HDL硬件描述性語言建模來分層次分模塊設計一個具有時分秒的電子鐘并能設置任意時刻鬧鐘,在ModelSim上仿真測試,最后在Cyclone IV E的FPGA實驗平臺上實際測試驗證。

本科畢業論文(設計) 題目: 基于FPGA的24小時數字鐘的設計 姓名: 專業: 學院: 學號: 導師: 職稱:

基于FPGA的24小時數字鐘設計

【摘要】介紹利用verilogHDL硬件描述語言結合FPGA(Field Programmable Gate Array)編程器件進行數字鐘的設計,并通過數碼管動態掃描顯示計時結果。本文采用分層次分模塊的方法,用verilog語言進行設計。在Quartus II 11.0開發平臺上完成設計,編譯,管腳分配,在ModelSim上仿真驗證,并在FPGA硬件上進行測試。該測試結果表明該設計方案切實可行。 【關鍵詞】FPGA;verilog;Quartus II 11.0;ModelSim;數字鐘 Design of digital clock 24 hours based on FPGA Medical imaging college of medical engineering professional level 2012 wangling student number: 1063451392 Instructor: he ling li 【abstract】Introducing the design of digital clock combined FPGA with verilogHDL,the time of clock can be displayed with the digital driving circuit.the project adopts the methods of Hierarchical modules to design with verilogHDL.the digital clock is designed,compiled and pin assignment on Quartus II 11.0 ,is simulated on ModelSim and is tested in the experiment box. The simulation waves and test results indicate that the project is feasible. 【key words】 FPGA; verilog; Quartus II 11.0; ModelSim; digital clock

目錄 基于FPGA的24小時數字鐘設計 引言 1.軟件與verilogHDL介紹 1.1軟件引入 1.2語言介紹 2.數字鐘的設計方案及原理 2.1設計方案 2.2設計原理 2.2.1數字鐘組成框圖 2.2.2數字鐘層次結構圖 3.核心模塊設計 3.1頂層模塊 3.2底層模塊 4.管腳分配 5.電路測試 6.注意事項 7.心得與體會 【參考文獻】 致謝 附錄

引言 隨著現代電子技術的發展,數字電子時鐘在家庭,車站,醫院,辦公等各個場所有著廣泛的應用,成為人們生活的必需品,由于生產工藝上的進步大大降低了現場可編程門陣列(FPGA)的成本,使其成為目前設計數字電路的首選器件之一[1]。電子時鐘的精度遠遠大于老式鐘表,而且在鐘表的報時能功能的基礎上不斷發展,諸如自動定時報警裝置,定時廣播,鬧鐘設置,甚至各種大型醫療設備的定時啟用,智能儀表,機器人,所有這些都是在數字鐘表的基礎上實現,為其他電路的設計提供一定借鑒作用[1]。因此對簡單數字鐘的研究有極大的意義。 1.軟件與verilogHDL介紹1.1軟件引入 Altera® Quartus® II設計軟件是適合單芯片可編程系統(SOPC)的最全面的設計環境[2]。建立工程項目和verilog HDL文件設計之后,可以使用 Quartus II 軟件中的 Settings 對話框、Assignment Editor 和 Floorplan Editor 指定初始設計約束條件,例如,引腳分配、器件選項和時序約束條件[2]。Quartus II還提供Compiler Settings 向導(Assignments 菜單)協助用戶指定初始設計的約束條件。 ModelSim仿真工具是Model公司開發的,它支持Verilog、VHDL以及他們的混合仿真,它可以將整個程序分步執行,使設計者直接看到程序下一步將要執行的語句,而且在程序執行的任何步驟任何時刻都可以查看任意變量的當前值。可以在Dataflow窗口觀察某一單元或模塊的輸入輸出連續變化等,比Quartus 自帶的仿真功能強大的多,支持Testbench,是目前業界最通用的仿真器之一[2]。 1.2語言介紹 Verilog語言形式簡單,與C語言相近,容易掌握,在門級開關電路描述方面比VHDL強的多[3]。相比傳統電路原理圖輸入法,verilogHDL設計周期短,無需專門的設計工具即可很輕松的將完成的設計移植到不同廠家的不同芯片中去[3],并在不同規模應用時比較方便的作修改調整。由于verilog HDL的信號位數是很容易改變的,故可對它進行修改來適應不同的規模你應用[4]。且在仿真驗證時,仿真測試文件可采用同一種描述語言來對設計電路進行測試。Verilog HDL 程序是由模塊構成的,每個模塊的內容都是嵌在module和endmodule兩個語句之間,每個verilog程序包括四個主要部分:端口定義,I/O說明,內部信號聲明,功能定義。每個模塊實現特定的功能,模塊是可以進行層次嵌套的。正因為如此,才可以將大型的數字電路設計分割成不同的小模塊來實現特定的功能,最后通過頂層模塊調用子模塊來實現整體功能[4]。

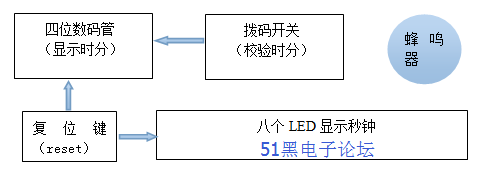

2.數字鐘的設計方案及原理2.1設計方案 本文以FPGA為實驗平臺,采用VerilogHDL語言在Quartus II 11.0開發環境下設計數字時鐘[5-6],具有計時,校時,整點報時的功能,具體功能為:1)能夠對小時、分鐘、秒鐘進行正常計時,每日按24小時計時制,能用四個七段式數碼管清晰顯示時和分,八個LED采用二進制形式來顯示秒鐘。2)具有復位功能,按下reset鍵可以對當前時間清零。3)校驗功能,能夠對數字鐘進行分時設置,方便在時鐘跑錯時進行校正。4)整點報時功能,當為12:00時和00:00時,蜂鳴器以1Hz的頻率響起12下,報整點功能實現。 數字鐘的硬件框圖如圖1所示。

圖1 數字鐘的硬件框圖 2.2設計原理2.2.1數字鐘組成框圖 數字時鐘組成框圖如圖2所示。可見,它由2個60進制計數器、1個24進制計數器和2個2選1數據選擇器共5個模塊組成。3個計數器共用一個時鐘信號CP,CP是50M系統時鐘分頻后的1Hz信號。在時和分的輸出端接上譯碼電路,用四個共陽極的七段數碼管顯示出時間[7] ,秒的輸出用8個LED的二進制形式來表示。兩個選擇器分別選擇時計數器和分計數器的使能控制信號,對時間進行校正時,在控制端(Adj_hour和Adj_min)的作用下,使能信號接高電平,此時每來一個時鐘信號,計數器加1計數,從而實現對小時和分鐘的校正[8]。正常計時時,使能信號來自于低位計數器的進位輸出,即秒計數達到59s時,產生輸出信號(Sco=1)使分計數器加1,分、秒計數器同時計時到最大值(59s 59min)時 ,產生輸出信號(Mco=1)使小時計數器加1。

圖2 數字鐘組成框圖(見51hei附件)

2.2.2數字鐘層次結構圖 數字時鐘的層次結構圖如圖3所示。可以看出,整個程序分為兩個層次4個模塊,其結構層次如圖2所示。底層由3個模塊組成,6進制計數器模塊(counter6.v)、10進制計數模(counter10.v)和24進制計數模塊(counter24.v),頂層有一個模塊(top_clock.v),它調用底層的3個模塊完成數字鐘的計時功能。

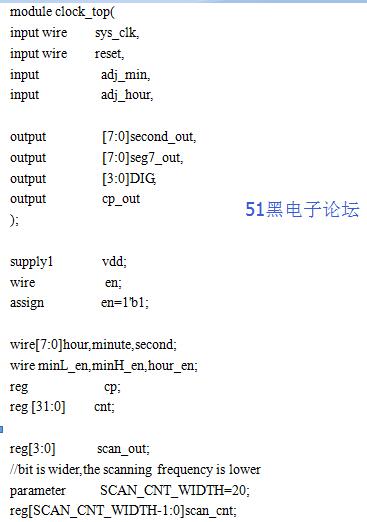

圖3數字鐘程序的層次結構圖 3.核心模塊設計3.1頂層模塊 建立數字時鐘工程new project clock,設計頂層模塊top_clock.v,頂層模塊包括1Hz分頻電路、整點報時電路、數碼管動態掃描(移位、選擇)、譯碼、顯示電路。其頂層框圖如圖4所示。

圖4 數字鐘頂層框圖

(1)生成1Hz時鐘信號模塊 時分秒計數器的計時時鐘cp為1Hz的信號,而系統時鐘信號(sys_clk)為50MHz,因此需要對50MHz信號進行分頻得到1Hz。具體分頻的代碼為: always@(posedge sys_clk or negedge reset) begin if(~reset)begin cnt<=0;cp<=0; end else begin if(cnt=25’d24999999)begin cp<=~cp;cnt<=0; end else begin cnt<=cnt+1; end end end (2)整點報時模塊 正常計數時,當分秒計數達到59分59秒,下一個時鐘信號cp的上升沿到來時蜂鳴器以1Hz的頻率發出蜂鳴實現整點報時,且N整點時,蜂鳴器就發出N聲“嘀”響,13時及13時以后的每個整點,蜂鳴器發出(N-12)聲“嘀”響。具體整點報時代碼為: assign hour_num=hour[7:4]*10+hour[3:0]+1; always@(posedge cp or negedge reset)begin if(~reset) bp_cnt_end<={5{1'b1}}; else if(hour_en) bp_cnt_end<=((hour_num==24)?12:(hour_num>=13)?(hour_num-12):hour_num)-1; end always@(posedge cp or negedge reset)begin if(~reset) bp_cnt<={5{1'b1}}; else if(hour_en) bp_cnt<=5'b0; else if(bp_cnt<bp_cnt_end) bp_cnt<=bp_cnt+1'b1; end always@(posedge cp or negedge reset)begin if(~reset) bp_enable<=1'b0; else if(hour_en) bp_enable<=1'b1; else bp_enable<=(bp_cnt<bp_cnt_end); end assign cp_out=scan_cnt[19] & bp_enable&cp;

(3)掃描信號模塊 數字鐘工作于正常時,每來一個時鐘信號sys_clk,reg [SCAN_CNT_WIDTH-1:0]scan_cnt進行動態掃描移位狀態(00,01,10,11)來選擇一個數碼管,只要掃描速度足夠快,利用發光二極管的余暉和人眼視覺的暫留作用,使人感覺每個數碼管都在顯示。具體掃描代碼為: always@(posedge sys_clk or negedge reset) begin if(~reset) scan_cnt<=0; else begin scan_cnt<=scan_cnt+1; end end always@(*) begin case(scan_cnt[SCAN_CNT_WIDTH-1:SCAN_CNT_WIDTH-2]) 2'b00:begin DIG_r<=4'b0001; scan_out<=minute[3:0];end 2'b01:begin DIG_r<=4'b0010; scan_out<=minute[7:4];end 2'b10:begin DIG_r<=4'b0100; scan_out<=hour[3:0];end 2'b11:begin DIG_r<=4'b1000; scan_out<=hour[7:4];end default:begin DIG_r<=4'b0000;scan_out<=4'b0;end endcase end

(4)選擇顯示數據及譯碼模塊 掃描信號決定某一時刻哪一個數碼管被點亮,掃描信號也是顯示時間數據的選擇信號。由于時間數據為BCD碼形式,需譯成七段顯示碼。具體代碼為: always@(*) begin case (scan_out) 0: seg7_out_r = 7'b0111111; // 0 1: seg7_out_r = 7'b0000110; // 1 2: seg7_out_r = 7'b1011011; // 2 3: seg7_out_r = 7'b1001111; // 3 4: seg7_out_r = 7'b1100110; // 4 5: seg7_out_r = 7'b1101101; // 5 6: seg7_out_r = 7'b1111101; // 6 7: seg7_out_r = 7'b0100111; // 7 8: seg7_out_r = 7'b1111111; // 8 9: seg7_out_r = 7'b1100111; // 9 10: seg7_out_r = 7'b1110111; // A 11: seg7_out_r = 7'b1111100; // b 12: seg7_out_r = 7'b0111001; // c 13: seg7_out_r = 7'b1011110; // d 14: seg7_out_r = 7'b1111001; // E 15: seg7_out_r = 7'b1110001; // F default: seg7_out_r = 7'b0000000; endcase end

(4)結果顯示模塊

assign seg7_out={1'b0,(~seg7_out_r[6:0])}; assign DIG=~DIG_r[3:0]; assign second_out=second[3:0]+second[7:4]*10;

(5)分時校驗模塊 使能端(en),復位(reset)為高電平時有效且計數器正常計時,分時校驗adj_min,adj_hour 為高電平時(本實驗開發板將撥碼開關撥到off狀態)停止計時此時數碼管處于調表狀態(每隔一秒數碼管分和時的數字顯示增加1且互不影響),分時校驗為低電平時計數器正常計時。具體分時校驗代碼為: assign minL_en=adj_min?vdd:(second==8'h59); assign minH_en=(adj_min&&(minute[3:0]==4'h9))||(minute[3:0]==4'h9)&&(second==8'h59); assign hour_en=adj_hour?vdd:((minute==8'h59)&&(second==8'h59)); 3.2底層模塊 設計6進制計數器模塊(counter6.v)、10進制計數器模塊(counter10.v)和24進制計數器模塊(counter24.v)。計數結果為BCD碼形式,通過調用這三個元件可以實現計時(當使能端en和ncr為高電平時,每來一個脈沖,計數器q加1直到計滿回零)。其各模塊框圖如圖5如下: 圖5 6、10、24進制模塊框圖

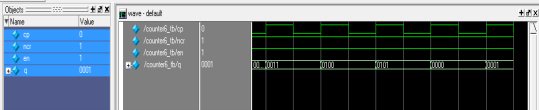

(1)6進制計數器模塊仿真波形及代碼實現  圖6 6進制計數波形 圖6 6進制計數波形

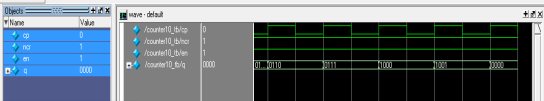

module counter6 (q,reset,en,cp); input cp,reset,en; output[3:0]q; reg[3:0]q; always@(posedge cp or negedge reset) begin if(~reset)q<=4'b0000; else if (~en)q<=q; else if(q==4'b0101)q<=4'b0000; else q<=q+1'b1; end endmodule (2)10進制計數器模塊仿真波形及代碼實現  圖7 10進制計數波形 圖7 10進制計數波形module counter10 (q,reset,en,cp); input cp,reset,en; output[3:0]q; reg[3:0]q; always@(posedge cp or negedge reset) begin if(~reset)q<=4'b0000; else if(~en)q<=q; else if(q==4'b1001)q<=4'b0000; else q<=q+1'b1; end endmodule (3)24進制計數器模塊仿真波形及代碼實現 圖8 24進制計數波形 module counter24(cntH,cntL,reset,en,cp); input cp,reset,en; output [3:0] cntH,cntL; reg[3:0]cntH,cntL; always@(posedge cp or negedge reset) begin if(~reset){cntH,cntL}<=8'h00; else if(~en) {cntH,cntL}<={cntH,cntL}; else if ((cntH>2)||(cntL>9)||((cntH==2)&&(cntL>=3))) {cntH,cntL}<=8'h00; else if ((cntH==2)&&(cntL<3)) begin cntH<=cntH; cntL<=cntL+1'b1; end else if(cntL==9) begin cntH<=cntH+1'b1; cntL<=4'b0000; end else begin cntH<=cntH; cntL<=cntL+1'b1; end end endmodule 4.管腳分配 選擇目標器件并對相應地引腳進行鎖定。在這里所選擇的器件為Altera公司Cyclone E系列的EP4C6E22C8芯片,引腳分配方法如表1。 注:在管腳分配時,FPGA的101引腳會出現出現Error: Can't place multiple pins assigned to pin location Pin_XX (IOC_X28_Y2_N0) 解決方法: Assignments->Device->Device and pin options->(卡)Dual purpose pin將nCE0以及Other Active Parallel Pins(其他復用的管腳)全部設置改為: “use as regular IO”默認只給FPGA下載使用選擇復用了就是下載完還可以給普通IO使用。

表1 引腳分配方法 5.電路測試 為驗證設計電路,最后將程序下載到FPGA開發板上進行硬件測試。下載目標器件選用Alter公司的Cyclone IV E系列的EP4C6E22C8芯片,用Quartus II 11.0 軟件進行電路綜合及程序下載。器件管腳設定后,將程序再編譯一次,最終生成可以下載的目標文件。將器件設定的相應管腳和數碼管驅動電路進行連接,最后將目標文件下載到器件當中,則數碼管顯示計時結果且能實現分時校驗。通過測試計時結果與分時校驗正確。

6.注意事項(1)實驗過程中發現數碼管部分管子的時不亮時微亮導致數字的顯示不清晰。分析數碼管的掃描頻率為系統脈沖50MHz,而FPGA數碼管的掃描頻率不支持太高頻率或者是數碼管的管腳不支持太高頻,而把掃描頻率降下來即可(本實驗采用增大掃描頻率的位寬,由于位寬定義的越大,掃描頻率越低)。程序改動如下: reg[7:0]scan_out改為reg[19:0]scan_out case(scan_cntt[7:6])改為case(scan_cnt[19:18]) 這樣即可解決數碼管顯示不清的問題。 - 在觀察實驗的過程中將if(cnt==24999999)改成if((cnt==25000000/k)-1)即可將時間走快k倍方便觀察實驗結果。

7.心得與體會 本次論文從查閱文獻,結合實際選題,軟件安裝到可實施方案的設計,VerilogHDL的編寫,由于是第一次做電子硬件功能設計: 首先:在設計思路上存在嚴重模糊,邏輯混亂,尤其在頂層模塊的設計時不能理清模塊之間的相互關系,對一些基本概念缺乏準確的認識; 其次:對軟件的安裝及操作環境的不熟悉導致實驗進行的緩慢; 第三:第一次倉促自學VerilogHDL語言常常犯一些低級的語法錯誤,即使是一個標點、匹配問題、數據類型定義錯了都會導致一連串的錯誤,故在編程時一定要倍加仔細; 第四:在仿真波形的觀察與分析上明顯感到專業知識的不夠,尤其在對分頻,掃描,譯碼,顯示電路這塊由于掃描頻率、延時單位、時間精度及運行時間沒有設計好導致無法觀察實驗意達到的波形及顯示結果; 第五:此次論文設計時間倉促且基礎不夠沒有進一步做數字時鐘的功能擴展; 第六:實驗是檢驗原理方案的唯一方法,只有通過不斷的嘗試、觀察、分析才能得到正確的實驗結果。 最后:此次論文也收獲很多,學習了數字系統自上而下的設計方法,進一步熟悉層次電路的設計方法。自頂而下的電子設計方法能使程序之間條理理清晰,分工明確,便于設計。同時也培養了自己動手設計實驗的能力及對計算機軟件編程應用方面的興趣也為今后的學習打好基礎。 【參考文獻】[1]康華光,鄒壽彬.《電子技術基礎數字部分(第五版)》[M].北京:高等教育出版社,2005144-146,162-163,121-133. [2]陳欣波.Alter FPGA 工程師成長手冊[M].北京:清華大學出版社,2012. [3]夏宇聞.verilog基本知識(下)[J].電子產品世界,2002,(20):87-90. [4]夏宇聞.《verilog數字系統設計教程》[M].北京:北京航空航天大學,2004年版. [5]紀欣然,丁一,梁致源.基于FPGA的多功能數字鐘設計[J]. 電子設計工程,2012,20(16):177-179. JI Xin-ran,DING Yi,LIANG Zhi-yuan.Design of multifunction digital clock based on FPGA [J].Electronic Design Engineering,2012,20(16):177-179. [6]徐大詔.基于FPGA實現的數字鐘設計[J].信息技術. [7]楊軍.基于FPGA的SOPC實踐教程[M].北京:科學出版社,2010. [8]王琥,任峻.基于FPGA的數字電子鐘設計[J].電子設計工程,2014,22(4):127-129

致謝 本次論文得以完成首先要感謝我的指導老師--何伶俐老師,從選題到寫作方向與思路再到整個論文的完成,在此期間不管大大小小的問題,只要我問到,何老師都會第一時間不厭其煩的為我解答。何老師認真負責的教學精神與樸實的品質深深的影響了我,告誡我科研來不得半點虛假,一定要腳踏實地是什么就是什么。其次,感謝參考文獻作者所提到的方法與觀點,正是因為閱讀了作者的相關著作讓我對層次電路的設計有了進一步的認識并逐漸熟悉了verilog語言的編程風格。然后我要感謝親愛的同學們,正是因為你們的陪伴與鼓勵使我變得堅強與勇毅,另外也非常感謝網上熱心論壇好友提供的幫助和解答。最后由于專業知識所限,論文中還存在很多瑕疵和需要研究改進的地方,望老師和同學予以指正。再次感謝四年來老師的諄諄教導,感謝同學的幫助與關心,祝福我的老師工作愉悅,闔家幸福,我的同學工作順利,勇攀高峰。

附錄(圖片)

(代碼)

…………

…………

完整的Word格式文檔51黑下載地址(內含清晰圖片與源代碼):

基于FPGA的數字電子時鐘設計與實現.doc

(6.21 MB, 下載次數: 211)

基于FPGA的數字電子時鐘設計與實現.doc

(6.21 MB, 下載次數: 211)

2018-4-2 13:53 上傳

點擊文件名下載附件

|