FPGA開發(fā)過程中,能夠方便的觀察模塊中信號(hào)的時(shí)序變化對(duì)邏輯的開發(fā)有很重要的意義。在quartus中的signal

tap

就是能夠方便的抓取模塊中的信號(hào),這類似與ISE的chipscope,但是在vivado中就沒有了,必須內(nèi)部例化ila,抓取的數(shù)據(jù)也不太方便,所以個(gè)人對(duì)vivado的使用還是感覺不太方便。言歸正傳,這里將詳細(xì)講解signal

tap的使用,我使用的quartus版本為10.1.

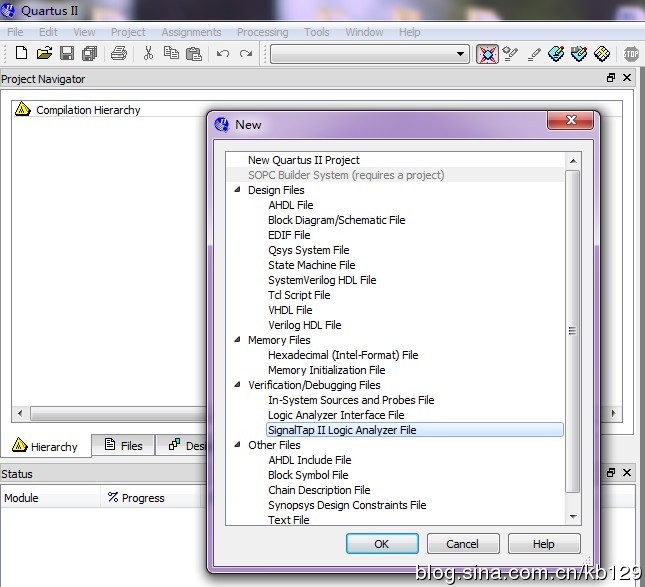

1.創(chuàng)建并設(shè)置STP文件

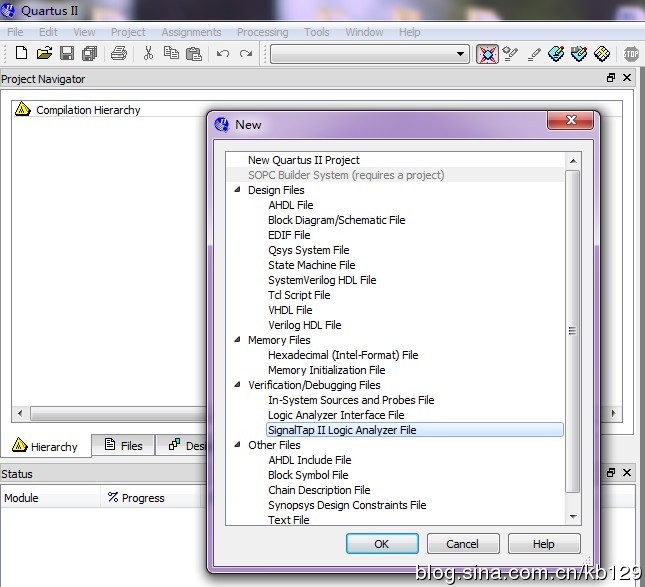

STP是signal tap的縮寫,在quartus界面中點(diǎn)擊file,選中new,彈出下面框:

選中SignalTap II

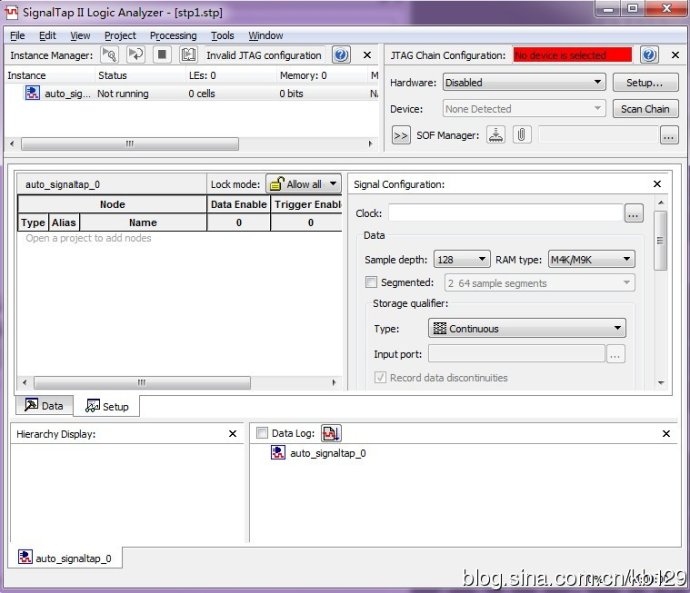

Logic A nalyzer File點(diǎn)擊OK,彈出下面框:

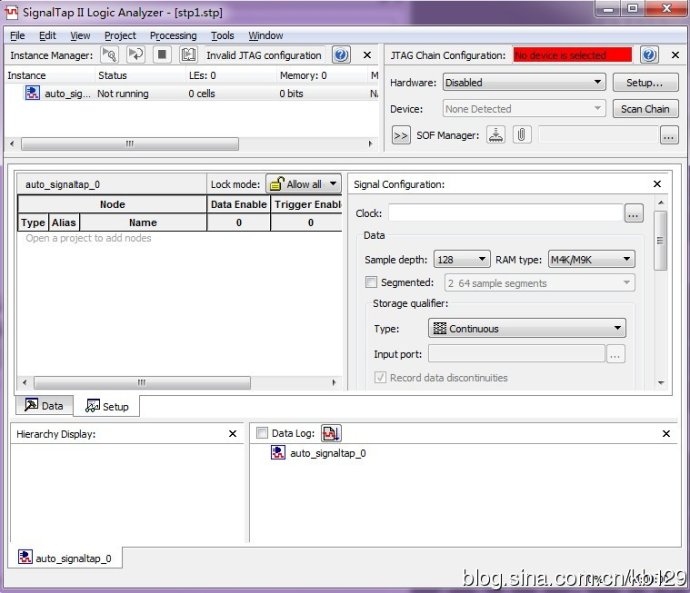

2.在STP文件中添加實(shí)例(instance)

添加方法:在上圖中的instance窗口中點(diǎn)擊右鍵,選擇create instance。

默認(rèn)情況下,STP中有一個(gè)默認(rèn)名為auto_signaltap_0的instance,雙擊auto_signaltap_0可以修改為自己定義的名字。

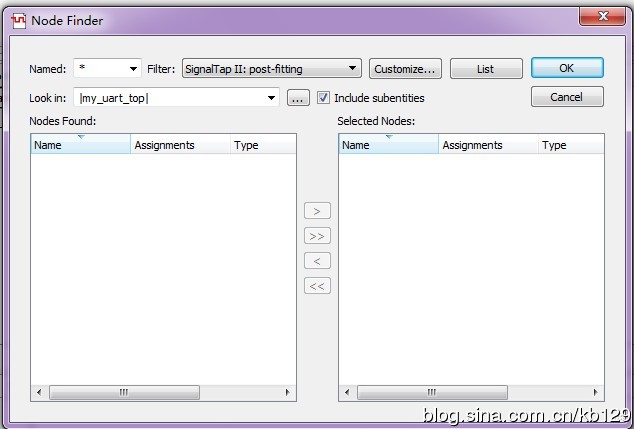

3.在instance中添加觀測(cè)節(jié)點(diǎn)(nodes)

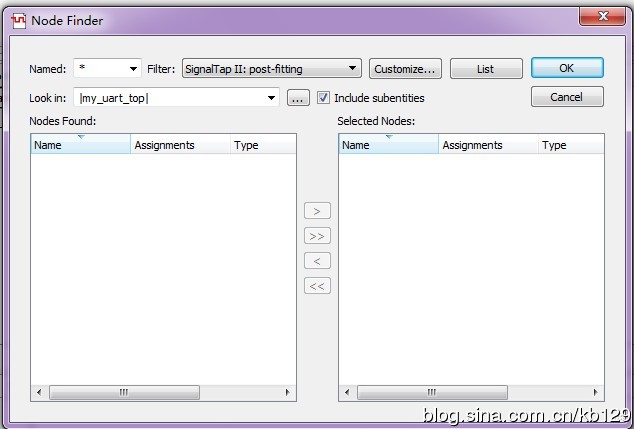

點(diǎn)擊Edit,選中Add Nodes...(此處有一個(gè)需要注意的:上面的步驟必須在打開一個(gè)工程后操作,否則Edit中的Add

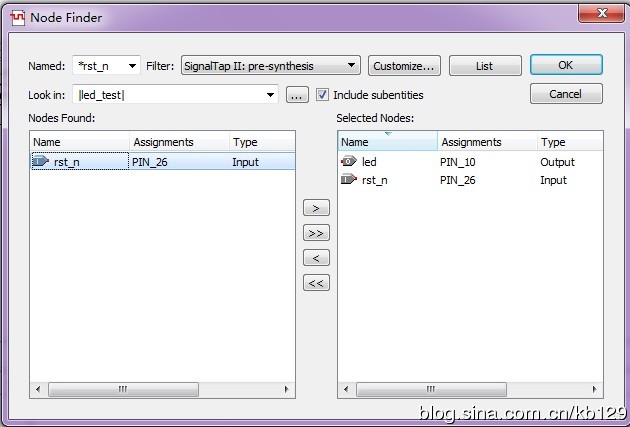

Nodes...將會(huì)是灰色,無法選中) ,然后彈出:

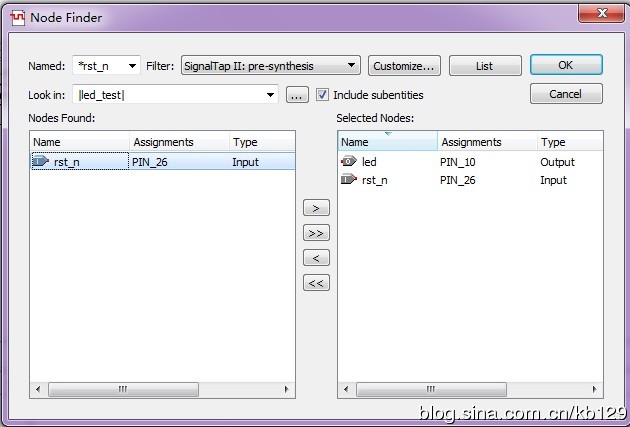

這個(gè)時(shí)候就需要添加你所需要抓取的信號(hào)。Look

in中選擇抓取的信號(hào)所在的模塊,F(xiàn)ilter修改為:

SignalTap

II:pre-synthesis.(這兩步非常重要,否則的話在Nodes

Found中會(huì)提示non-mathcad),在Named中輸入所需抓取的信號(hào)名(貌似必須是全名),點(diǎn)擊List,在Nodes

Found中就會(huì)出現(xiàn)該信號(hào),雙擊該信號(hào),該信號(hào)就會(huì)出現(xiàn)在Selected

Nodes里面。同樣在Named中輸入另外需要抓取的信號(hào),使之出現(xiàn)在Selected

Nodes里面。添加完所有的信號(hào)后,點(diǎn)擊OK。

4.為instance添加采樣時(shí)鐘

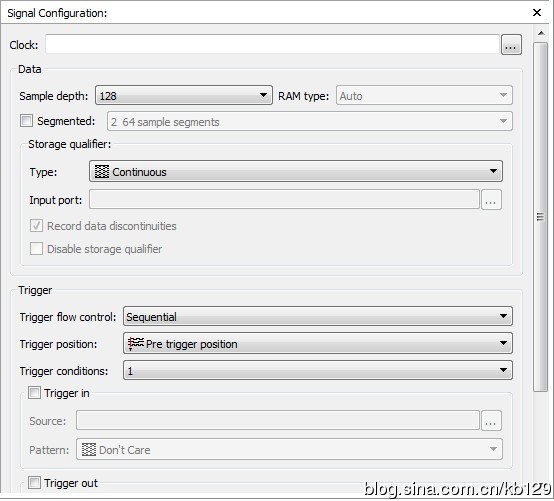

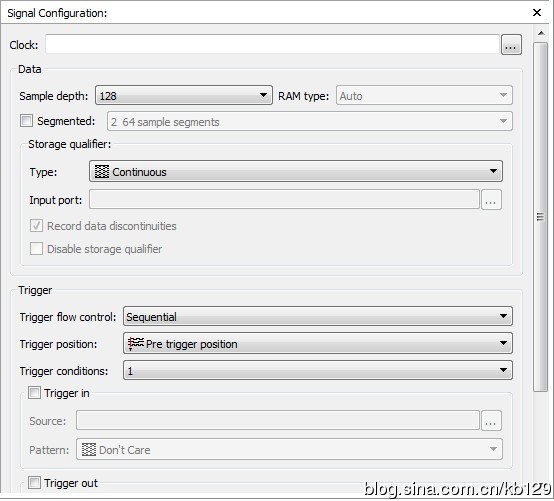

點(diǎn)擊軟件中下部的Setup按鍵,在右邊會(huì)出現(xiàn):

點(diǎn)擊上圖的clk旁邊的[...]將會(huì)彈出與上面一樣的Noder

Finder窗口,選擇好合適的時(shí)鐘信號(hào)。然后設(shè)置一些基本的參數(shù):

采樣深度,Sample depth

個(gè)人建議選大些,但是又不能超過FPGA資源,不然在后面的編譯會(huì)報(bào)錯(cuò)。

RAM類型,這個(gè)默認(rèn)為auto,不用管

觸發(fā),Trigger 這個(gè)在初期使用signal

tap就選擇默認(rèn),后期可以根據(jù)具體信號(hào)波形來設(shè)置。

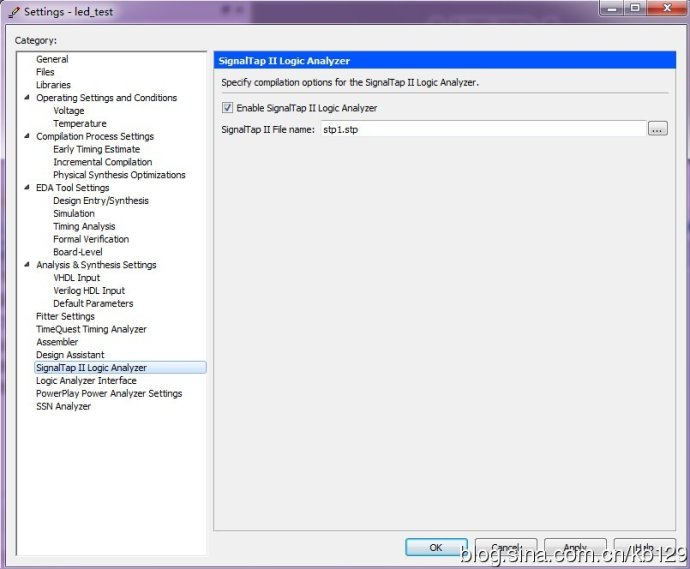

5.重新編譯添加了signal tap工程

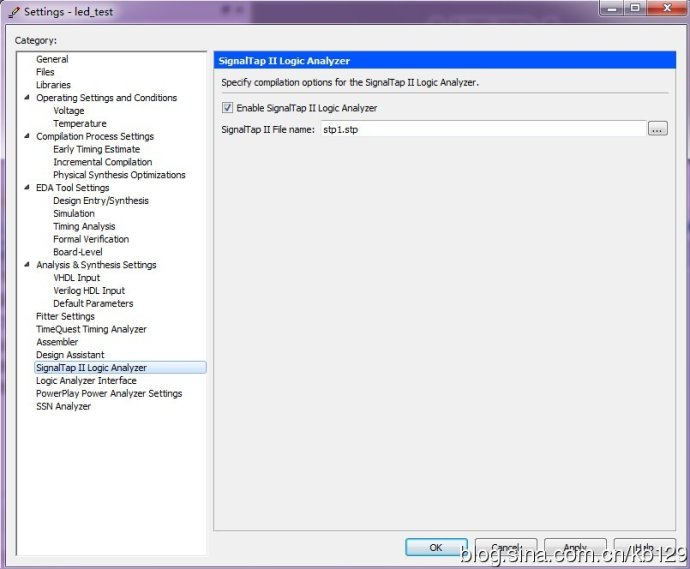

在quartus10.1中一般在上面的步驟都做好后,關(guān)閉signal

tap窗口一直點(diǎn)擊OK就行。為了確保工程中的確添加了我們剛剛新建的stp文件,可以打開工程,選中Entity中的頂層,右鍵點(diǎn)擊settings,就會(huì)出現(xiàn):

選中左邊的SignalTap II Logic

Analyzer,在右邊[...]選中剛剛新建的stp文件。

6.編譯和下載代碼

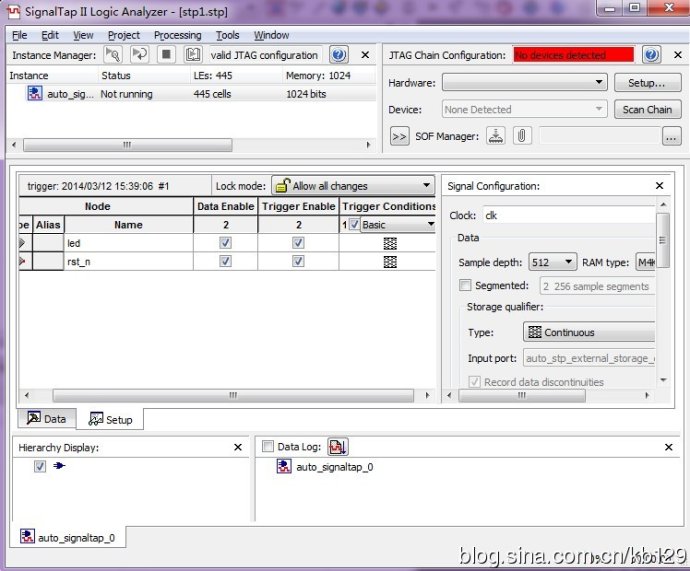

按照一般的方法,編譯和生成sof文件。下載代碼需要在SignalTap

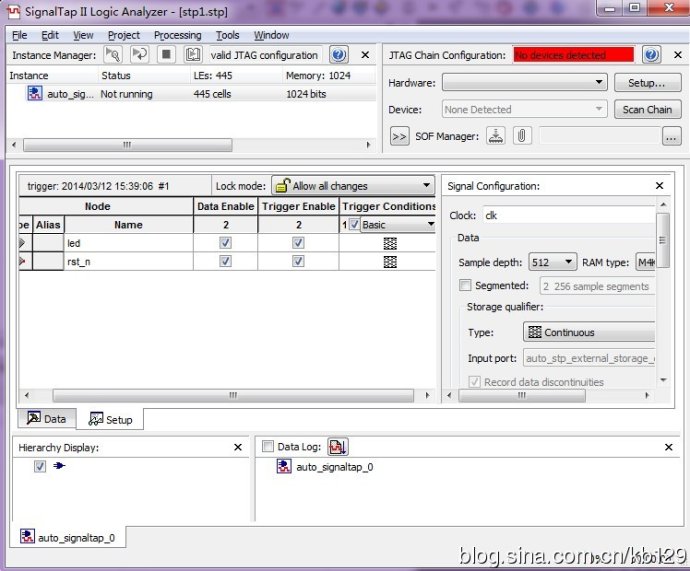

II 中下載,雙擊stp文件,就會(huì)彈出:

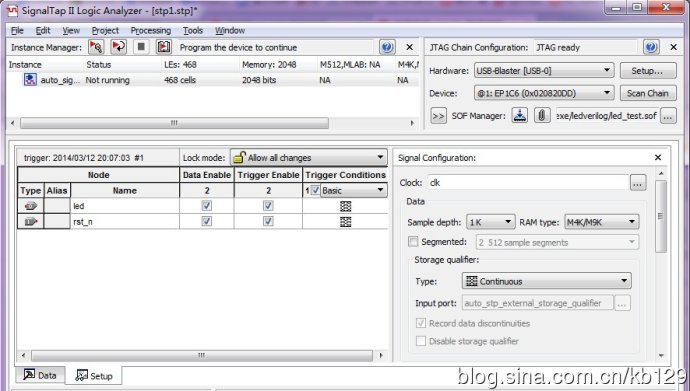

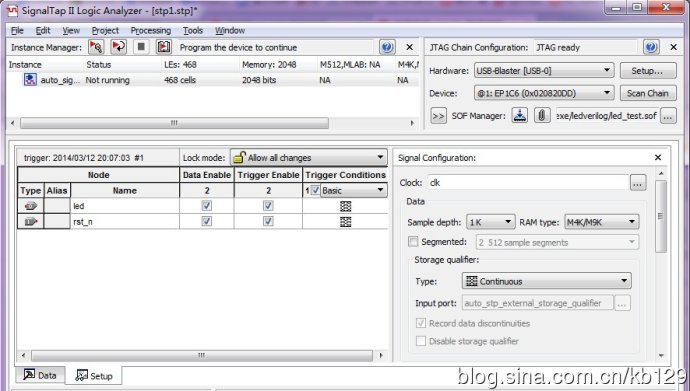

給板子上電,并且連上JTAG線(有的稱為仿真器)。界面就會(huì)變成:

點(diǎn)擊右上角的SOF Manager后面的[...],選擇好剛剛生成的SOF文件,然后點(diǎn)擊program

device。

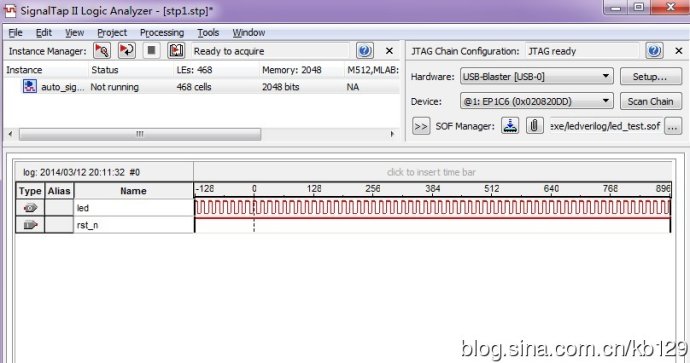

7.抓取數(shù)據(jù),觀測(cè)波形

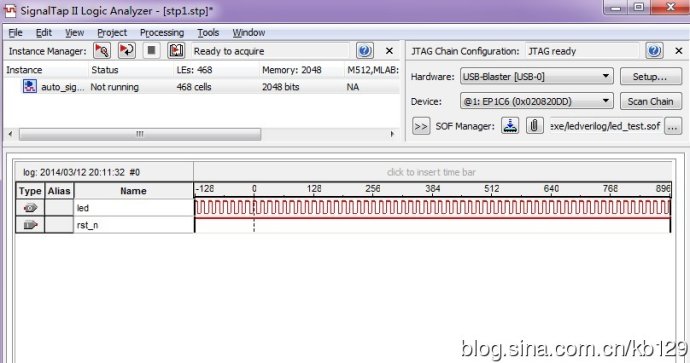

在下載好sof后,點(diǎn)擊Instance Manager旁邊的run

analyzer(也就是紅色的三角標(biāo)志),就會(huì)彈出:

界面上就是抓取出來的信號(hào)波形,此時(shí)完成了signal

tap的基本操作。

理論分析:

1.SignalTap II 的優(yōu)缺點(diǎn)(摘自《altera

FPGA/CPLD設(shè)計(jì)(基礎(chǔ)篇)》(第2版))

優(yōu)點(diǎn):

1.不占用額外的I/O管腳

2.不占用PCB上的空間

3.不破壞信號(hào)的完整性

4.相對(duì)傳統(tǒng)邏輯分析儀設(shè)備,SignalTap II

免費(fèi)試用。

缺點(diǎn):SignalTap II

中抓取數(shù)據(jù)的深度取決于RAM剩余大小,特別是在低端的FPGA中,特別是學(xué)習(xí)板中,由于RAM太小,抓取的數(shù)據(jù)太少,SignalTap

II 基本對(duì)設(shè)計(jì)沒有幫助。

2.觸發(fā)位置的選擇

以前似乎有四種選擇,現(xiàn)在好像只能找到三種:

1.Pre trigger

position

:采樣的數(shù)據(jù)12%為觸發(fā)前,88%為觸發(fā)后

2.Center trigger position

:采樣的數(shù)據(jù)50%為觸發(fā)前,50%為觸發(fā)后

3.Post

trigger

position

:采樣的數(shù)據(jù)88%為觸發(fā)前,12%為觸發(fā)后