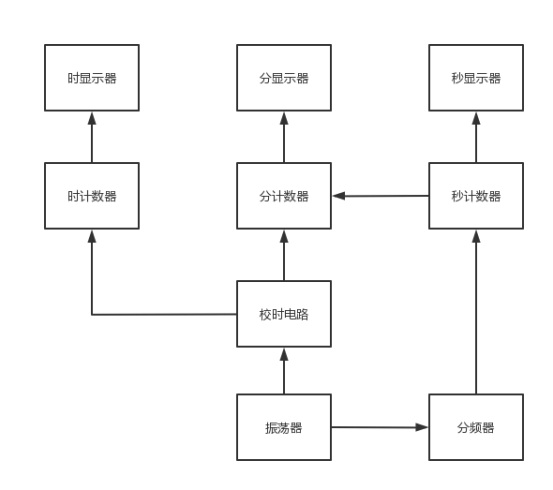

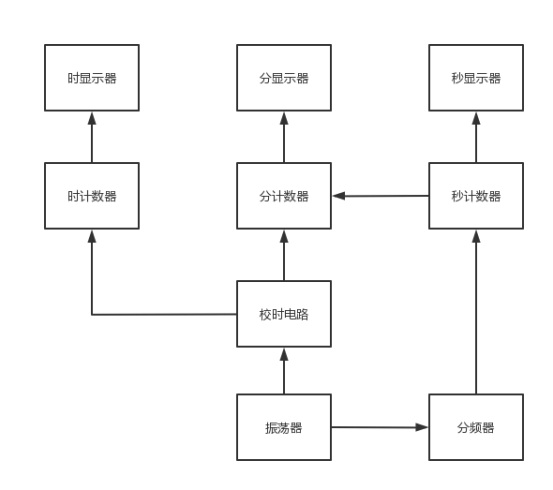

數字鐘電路的基本組成框架圖如圖一所示,它主要由多諧振蕩器、計數器、譯碼器和數碼顯示器4個部分組成。

圖一 數字鐘電路的基本組成(方框圖)

2、設計方案數字鐘是一個將“時”,“分”,“秒”顯示于人的視覺器官的計時設計裝置。他的計時周期為24小時,顯示滿刻度為23時59分59秒。因此,一個基本的數字鐘電路主要由譯碼顯示器、“時”,“分”,“秒”,計數器、校時電路和振蕩器組成。數字鐘實際上是一個對標準頻率進行計數的計數電路,由于計數的起始時間不可能與標準時間一致,故需要在電路上加一個校時電路,同時標準的1HZ時間信號必須做到準確穩定,通常使用石英晶體振蕩器電路。

三、單元電路設計與參數計算1、單元電路的設計1.1時鐘模塊

考慮到數字鐘對精度要求較高,故時鐘模塊是由555計時器組成的振蕩電路,其在電路中直接產生頻率為1HZ的脈沖信號。圖3.1.1為由555計時器所構成的。

圖3.1.1時鐘模塊

1.2分頻計數器

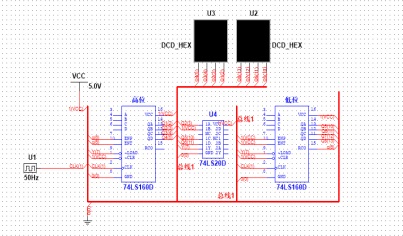

設計的60和24進制加法計數器都大于一個74LS160N的計數范圍,所以需要級聯。當且僅當秒的個位計數到10的瞬間,即輸出為1010時,向本位發送一個清零信號,并同時向十位發送一個進位脈沖。但由于74LS160N的清零方式為異步清零,這種清零方式會導致清零的不可靠。所以必須要把脈沖調整到一個較低的周期,才會產生有效地清零和進位信號。兩片74LS160N的預置是同步的,利用預置端的ABCD四個端口來實現清零。把A-D接地后,當置入控制器LOAD為低電平時,在CLK上升沿作用下,輸出端QA-QD會與數據輸入端A-D相一致。通過采用預置的方式,可以確保清零的穩定。但為了使清零和進位同步進行,在清零的輸出端需要引出一根線,加上非門引入下一級計數器的輸入端。這種可以實現多重清零的方式,也可以實現24進制用10進制顯示,而且清零和進位的可靠性與同步性得到了極大地提高。

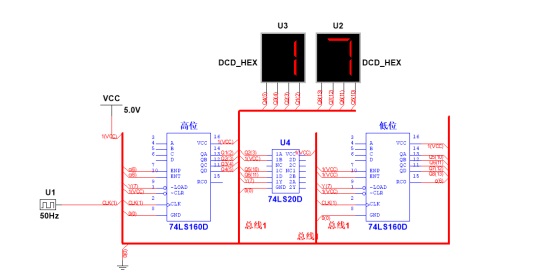

1.3秒計數器

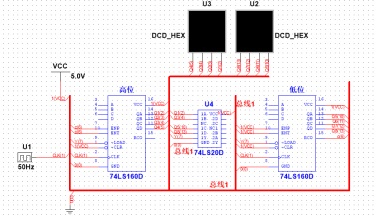

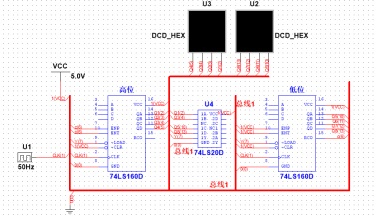

由于時鐘模塊分頻后可直接產生1Hz的標準脈沖時鐘信號,所以可以直接把所得的1Hz信號作為秒位計數器的時鐘信號。使用兩片同步加法計數器74LS160N構成60進制加法計數器作為秒計時器,同時在設計的時候,也應用到了74LS20N這個雙4輸入與非門集成電路,其在電路中充當與非門的作用。在秒的個位計數到10的瞬間,向十位發送一個進位脈沖。秒的十位加法計數器在計數到6的瞬間,向74LS20N發送清零信號。這樣就構成了一個級聯而形成的60進制帶進位與清零的加法計數器。圖3.1.3為秒計時器的電路圖。

圖3.1.3秒計數器

1.4分計數器

按照同樣的方法,可以構成分位的計數器。圖3.1.4為秒計時器的電路圖。

圖3.1.4分計數器

1.5時計數器

秒分頻計數器采用兩片74LS160和一片74LS20組成,74LS160是十進制計數器,也就是說只能記住十個數字,計數完成后自動清零,同時產生一個進位信號,而74LS20內部由兩組4輸入與非門組成;秒分頻計數器是60進制的計數器當低位的![]() 變為0011的同時高位的

變為0011的同時高位的![]() 變為0010時,將高位和低位各置1的引腳接入到74LS20的一組四輸入與非門中,此時74LS20輸出低電平,將其接入兩片74LS160的置零端從而完成兩片計數器的同步置零。

變為0010時,將高位和低位各置1的引腳接入到74LS20的一組四輸入與非門中,此時74LS20輸出低電平,將其接入兩片74LS160的置零端從而完成兩片計數器的同步置零。

圖3.1.5為秒計時器的電路圖。

圖3.1.5時計數器

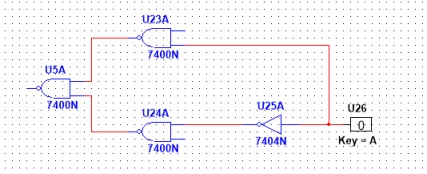

1.6校時電路

當數字鐘走時出現誤差時,需要校正時間。校時電路實現對“時”“分”“秒”的校準。在電路中設有正常計時和校對位置。本實驗實現“時”“分”“秒”的校對。

對校時的要求是,在小時校正時不影響分和秒的正常計數;在分校正時不影響秒和小時的正常計數,在秒校正時不影響分和小時的正常計數。圖3.1.6為校時電路。

圖3.1.6校時電路

1.7顯示模塊

現在的許多電器設備上都有顯示十進制字符的字符顯示器,以直觀的顯示出電器設備的運行數據。目前廣泛使用的字符顯示器是七段字符顯示器,或稱七段數碼管。常見的七段數碼管有液晶顯示數碼管和半導體數碼管兩種。 半導體數碼管是由七段發光二極管(Light Emitting Diode)組成,簡稱LED。圖3.1.7是

LED的引腳及其等效電路。

圖3.1.7LED的引腳及其等效電路

顯示計數結果需要用到顯示譯碼器DCD_ HEX,如圖3.1.7.1

![]()

圖3.1.7顯示譯碼器DCD_ HEX

2、元件參數的計算2.1時鐘模塊

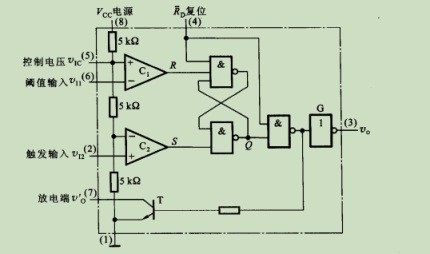

555定時器的內部電路由分壓器、電壓比較器![]() 和

和![]() 、簡單SR鎖存器、放電三極管T以及緩沖器G組成,其內部結構圖如圖3.2.1所示。

、簡單SR鎖存器、放電三極管T以及緩沖器G組成,其內部結構圖如圖3.2.1所示。

圖3.2.1 555定時器內部結構圖

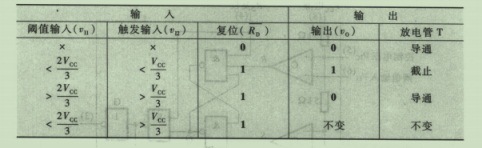

555定時器的功能表如下表所示

555定時器功能表

用555定時器組成多諧振蕩器時,在接通電源后,電容C被充電,當![]() 上升到

上升到![]() 時,使

時,使![]() 為低電平,同時放電三極管

為低電平,同時放電三極管![]() 導通,此時電容C通過

導通,此時電容C通過![]() 和

和![]() 放電,

放電,![]() 下降。 當

下降。 當![]() 下降到

下降到![]() 時,

時,![]() 翻轉為高電平。電容器C放電所需的時間為

翻轉為高電平。電容器C放電所需的時間為

![]()

當放電結束時,T截止,![]() 將通過

將通過![]() 、

、![]() 向電容器C充電,

向電容器C充電,![]() 由

由![]() 上升到

上升到![]() 所需要的時間為

所需要的時間為

![]()

當![]() 上升到

上升到![]() 時,電路又翻轉為低電平。如此周而復始,于是,在電路的輸出端就得到一個周期性的矩形波。其振蕩頻率為

時,電路又翻轉為低電平。如此周而復始,于是,在電路的輸出端就得到一個周期性的矩形波。其振蕩頻率為

![]()

當我們要在電路中由555振蕩電路直接產生頻率為1Hz的脈沖信號時,555振蕩器的參數確定:T=0.7(R1+R2)C=500ms,f=1/t=2HZ,所以參數可以確定為:C1=47uF,C2=10nF,R1=10KΩ,R2=10KΩ。

2.2秒計數器

秒分頻計數器采用兩片74LS160和一片74LS20組成,74LS160是十進制計數器,也就是說只能記住十個數字,計數完成后自動清零,同時產生一個進位信號,而74LS20內部由兩組4輸入與非門組成;秒分頻計數器是60進制的計數器當低位的![]() 變為1010的同時高位的

變為1010的同時高位的![]() 變為0101時,將高位和低位各置1的引腳接入到74LS20的一組四輸入與非門中,此時74LS20輸出低電平,將其接入兩片74LS160的置零端從而完成兩片計數器的同步置零。

變為0101時,將高位和低位各置1的引腳接入到74LS20的一組四輸入與非門中,此時74LS20輸出低電平,將其接入兩片74LS160的置零端從而完成兩片計數器的同步置零。

2.3分計數器

分的個位和十位計數單元的狀態轉換和秒的是一樣的,只是它要把進位信號傳輸給時的個位計數單元。

2.3時計數器

秒分頻計數器采用兩片74LS160和一片74LS20組成,74LS160是十進制計數器,也就是說只能記住十個數字,計數完成后自動清零,同時產生一個進位信號,而74LS20內部由兩組4輸入與非門組成;秒分頻計數器是60進制的計數器當低位的![]() 變為0011的同時高位的

變為0011的同時高位的![]() 變為0010時,將高位和低位各置1的引腳接入到74LS20的一組四輸入與非門中,此時74LS20輸出低電平,將其接入兩片74LS160的置零端從而完成兩片計數器的同步置零。

變為0010時,將高位和低位各置1的引腳接入到74LS20的一組四輸入與非門中,此時74LS20輸出低電平,將其接入兩片74LS160的置零端從而完成兩片計數器的同步置零。

2.4校時電路

剛接通電源或走時不準時,都需要進行時間校準。理論上校時電路是可以通過直接與脈沖源相接而獲得脈沖頻率。但是因為實物電路的硬件緣故。在按下和彈開按鈕的瞬間,數碼管的數字會因為按鈕的接觸原因而抖動。這就導致了在較好之間后想結束校時,因為按鈕抖動的原因,時間又改變了。相當于無校時功能。實現校時電路的方法有很多,采用基本R-S觸發器構成單脈沖發生器是其中的一種。RS觸發器具有置位、復位和保持(記憶)的功能,可以消除抖動,所以決定用這個比較簡單的校時電路。

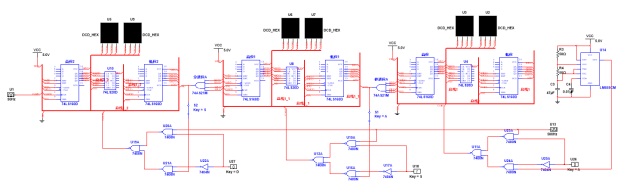

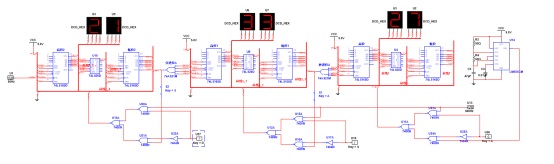

4、總原理圖1. 總原理圖總原理圖如圖4.1所示

圖4.1總原理圖

2. 總原理圖分析1.1總體仿真電路1

1.2總體仿真電路2

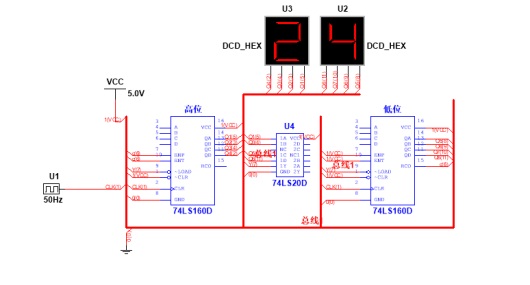

2.1秒計數器仿真分析

圖5.2.1為秒計數器仿真分析

圖5.2.1秒計數器仿真分析

分析結果為秒計數器的功能能夠正常實現。

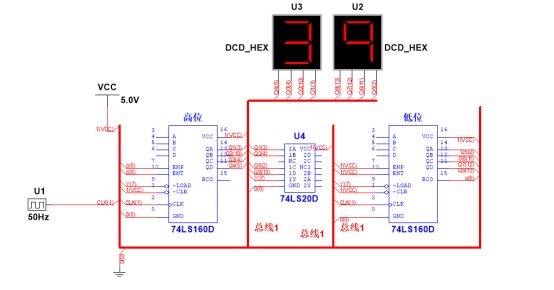

2.2分計數器仿真分析

圖5.2.2為分計數器仿真分析

圖5.2.2分計數器仿真分析

分析結果為分計數器的功能能夠正常實現。

2.3時計數器仿真分析

圖5.2.3為時計數器仿真分析

圖5.2.3時計數器仿真分析

分析結果為時計數器的功能能夠正常實現。

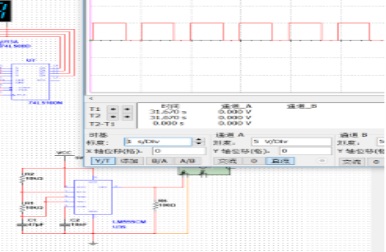

2.4555振蕩器仿真分析

圖5.2.4為555振蕩器仿真分析

圖5.2.4 555振蕩器仿真分析

分析結果為555振蕩器的功能能夠正常實現。

本人初學,僅供參考,存在錯誤和不足之處,請大家回帖多多指教,切勿照搬,文件下載:

數字鐘Multisim仿真和文檔.7z

(1.91 MB, 下載次數: 108)

數字鐘Multisim仿真和文檔.7z

(1.91 MB, 下載次數: 108)

| 歡迎光臨 (http://www.raoushi.com/bbs/) | Powered by Discuz! X3.1 |