��(bi��o)�}: VHDL�Z(y��)�Ԕ�(sh��)��ʽ�l��Ӌ(j��)���O(sh��)Ӌ(j��)�^(gu��)�̣�Դ���a���ͷ���D��(Word�ęn) [��ӡ���(y��)]

����: ͯ�ԟo(w��)�� �r(sh��)�g: 2019-1-22 16:16

��(bi��o)�}: VHDL�Z(y��)�Ԕ�(sh��)��ʽ�l��Ӌ(j��)���O(sh��)Ӌ(j��)�^(gu��)�̣�Դ���a���ͷ���D��(Word�ęn)

���Ľ�B��ʹ��VHDL�_(k��i)�l(f��)FPGA��һ�����̣����c(di��n)��B���l��Ӌ(j��)�Ļ���ԭ��������(y��ng)�Ĝy(c��)����������K������һ�N����FPGA�Ĕ�(sh��)���l�ʵČ�(sh��)�F(xi��n)������ԓ�O(sh��)Ӌ(j��)����Ӳ�������Z(y��)��VHDL����ܛ���_(k��i)�l(f��)ƽ�_(t��i)ISE����ɣ��������^���ٕr(sh��)��l�ʣ�100MHz��������������ԓ�O(sh��)Ӌ(j��)���l��Ӌ(j��)�ܜ�(zh��n)�_�Ĝy(c��)���l����1Hz��100MHz֮�g����̖(h��o)��ʹ��ModelSim����ܛ����(du��)VHDL�������˷��棬������˾C�ϲ��ֲ�������K���d��оƬSpartan-II��ȡ�����Üy(c��)ԇЧ����

ԭ����D

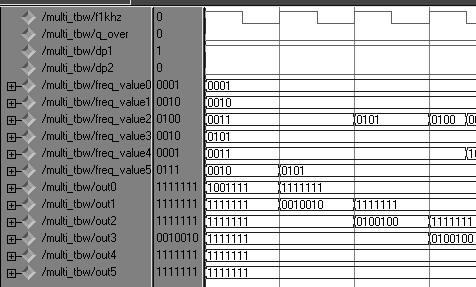

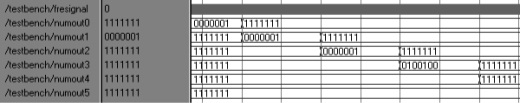

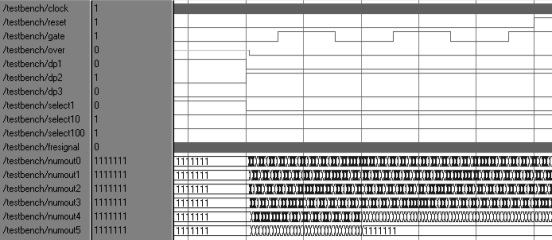

�y(c��)ԇ�Y(ji��)��

�����īI(xi��n)

Ӌ(j��)��(sh��)����(j��)(li��n)����

�i����Դ����

플�ԭ��D

Ӌ(j��)��(sh��)���ļ�(j��)(li��n)�D

�����Y��ԭ��

���g�ĸ�

��һ�� ����

�ڶ��� ����FPGA��VHDL�O(sh��)Ӌ(j��)����

2.1 ����

2.2 VHDL�Z(y��)�Խ�B

2.2.1 VHDL�����c(di��n)

2.2.2 ����VHDL����������O(sh��)Ӌ(j��)����

2.3 FPGA�_(k��i)�l(f��)��B

2.3.1 FPGA��(ji��n)��

2.3.2 FPGA�O(sh��)Ӌ(j��)����

2.3.3 Spartan-IIоƬ��(ji��n)��

������ ��(sh��)���l��Ӌ(j��)��ܛ���_(k��i)�l(f��)�h(hu��n)��

3.1 �_(k��i)�l(f��)�h(hu��n)��

3.2 ModelSim��B

3.2.1 ISE�h(hu��n)����ModelSim��ʹ��

3.3 ISE��B

3.3.1 �����(xi��ng)Ŀ����

3.3.2 �����

3.3.3 ����플�ԭ��D

3.3.4 �C��

3.3.5 ���ֲ���

3.3.6 ���d��Ӳ������

������ ��(sh��)���l��Ӌ(j��)���O(sh��)Ӌ(j��)�c��(sh��)�F(xi��n)

4.1 �΄�(w��)Ҫ��

4.2 �y(c��)��ԭ��

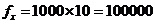

4.2.1 �l�ʻ�r(sh��)�g��ԭʼ����(zh��n)

4.2.2 ���Ӌ(j��)��(sh��)���y(c��)�l����

4.2.3 �`�����

4.2.4 �y(c��)�����ڵı�Ҫ�Ժͻ���ԭ��

4.2.5 �Ⱦ��Ȝy(c��)��

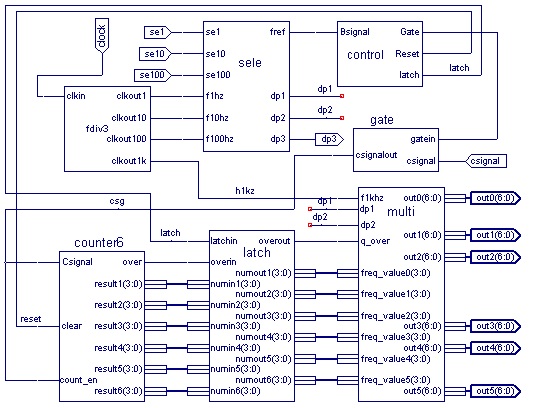

4.3 ԭ����D

4.4 ��ģ�K�Ĺ��ܼ���(sh��)�F(xi��n)

4.4.1 ���l��

4.4.2 �l�T(m��n)�x����

4.4.3 �y(c��)�l������

4.4.4 �l��Ӌ(j��)��(sh��)��

4.4.5 �i����

4.4.6 �����@ʾ�����g�aϵ�y(t��ng)

4.5 플�ԭ��D

4.6 �������_�����d��(sh��)�F(xi��n)

4.7 �y(c��)ԇ�Y(ji��)��

������ �Y(ji��)Փ

�����īI(xi��n)

�� �x

�� �

���1. Ӌ(j��)��(sh��)����(j��)(li��n)����

���2. �i����Դ����

���3. 플�ԭ��D

���4. Ӌ(j��)��(sh��)���ļ�(j��)(li��n)�D

�����Y��ԭ��

���g�ĸ�

����Ӽ��g(sh��)�I(l��ng)���(n��i)���l����һ��(g��)������ą���(sh��)���l���c�����S��늅����Ĝy(c��)���������y(c��)���Y(ji��)������ʮ�����е��P(gu��n)ϵ����r(sh��)�g���ٶȵȶ��漰���������D(zhu��n)�����l�ʵĜy(c��)������ˣ��l�ʵĜy(c��)�����@�ø�����Ҫ�����ң�Ŀǰ����Ӝy(c��)���У��l�ʵĜy(c��)�����_������ߵ�.�F(xi��n)���Ј�(ch��ng)���и��N��ܣ��߾��ȣ����l�ʵĔ�(sh��)���l��Ӌ(j��)�����r(ji��)�ơ����ڌ�(sh��)�H�����У����nj�(du��)������̖(h��o)���l�ʜy(c��)����Ҫ���_(d��)���dz��ߵľ��ȡ���ˣ����������һ�N�ܝM��һ��y(c��)������Ҫ���ɱ������Ĕ�(sh��)���l��Ӌ(j��)���O(sh��)Ӌ(j��)������

������Ҫ�΄�(w��)��ᘌ�(du��)�O(sh��)Ӌ(j��)��Ҫ����FPGA����Ӳ�������Z(y��)��VHDL��ɔ�(sh��)���l��Ӌ(j��)���O(sh��)Ӌ(j��)��ͨ�^(gu��)���棬�������C�ϲ���K���d��FPGA����ȥ��(sh��)�F(xi��n)�������y(c��)��̖(h��o)�����β��֡��Iݔ�벿�����⣬����ȫ����һƬF(xi��n)PGAоƬ�ό�(sh��)�F(xi��n)������(g��)ϵ�y(t��ng)�dz�����(ji��n)�����Ҿ����`��ĬF(xi��n)��(ch��ng)�ɸ����ԡ��ڲ�����Ӳ���·�Ļ��A(ch��)�ϣ���(du��)ϵ�y(t��ng)�M(j��n)�и��N���M(j��n)߀�����M(j��n)һ�����ϵ�y(t��ng)�����ܡ�ԓ��(sh��)���l��Ӌ(j��)���и��١����_���ɿ������ɔ_�ԏ�(qi��ng)�ͬF(xi��n)��(ch��ng)�ɾ��̵ȃ�(y��u)�c(di��n)����(j��ng)��(sh��)�(y��n)��������y(c��)�����Ȼ������_(d��)������ϵ�y(t��ng)�ɱ��dz�������������W(xu��)����(sh��)��߉�O(sh��)Ӌ(j��)�C�ό�(sh��)�(y��n)�����Ɣ�(sh��)���l��Ӌ(j��)�Ă��x������

�ڶ��� ����FPGA��VHDL�O(sh��)Ӌ(j��)����2.1 ������(sh��)���l��Ӌ(j��)�ǔ�(sh��)���·�е�һ��(g��)���͑�(y��ng)�ã���(sh��)�H��Ӳ���O(sh��)Ӌ(j��)�õ��������^�࣬�B�����^��(f��)�s�����ҕ�(hu��)�a(ch��n)�����^����ӕr(sh��)����ɜy(c��)���`��ɿ��Բ�l��Ӌ(j��)���O(sh��)Ӌ(j��)�Ђ��y(t��ng)�����ͬF(xi��n)�����������y(t��ng)���O(sh��)Ӌ(j��)�����ĕr(sh��)�Ĺ����O(sh��)Ӌ(j��)��(qi��ng)�ȴ������׳��e(cu��)���O(sh��)Ӌ(j��)���|(zh��)����һ������õġ���Ȼ�҂����]���F(xi��n)������������ʮ���o(j��)��ʮ����d�������O(sh��)Ӌ(j��)�Ԅ�(d��ng)�����g(sh��)��Ӣ�Ğ�Electronic Design Auto���s��(xi��)��EDA����EDA�O(sh��)Ӌ(j��)�����У��õ���V������VHDL��VERILOG����(d��ng)Ȼ߀�������ġ����^VHDL��VERILOG����플��O(sh��)Ӌ(j��)����VHDL��(y��u)��VERILOG�����T(m��n)��(j��)�·�O(sh��)Ӌ(j��)����VERILOG��(y��u)��VHDL���S����(f��)�s�ɾ���߉������CPLD���ďV����(y��ng)�ã���EDA���������_(k��i)�l(f��)�ֶΣ��\(y��n)��VHDL�Z(y��)�ԣ���ʹ����(g��)ϵ�y(t��ng)���(ji��n)����������w�����ܺͿɿ��ԡ����ε��l��Ӌ(j��)�O(sh��)Ӌ(j��)��Ҫ��플��O(sh��)Ӌ(j��)��Ŀ�����O(sh��)Ӌ(j��)6λʮ�M(j��n)���l��Ӌ(j��)���W(xu��)��(x��)���õĔ�(sh��)��ϵ�y(t��ng)�O(sh��)Ӌ(j��)����������VDHL�����O(sh��)Ӌ(j��)��(sh��)�F(xi��n)�Ĕ�(sh��)���l��Ӌ(j��)�������y(c��)��̖(h��o)�����β��֡��Iݔ�벿�����⣬����ȫ����һƬF(xi��n)PGAоƬ�ό�(sh��)�F(xi��n)������(g��)ϵ�y(t��ng)�dz�����(ji��n)�����Ҿ����`��ĬF(xi��n)��(ch��ng)�ɸ����ԡ��ڲ�����Ӳ���·�Ļ��A(ch��)�ϣ���(du��)ϵ�y(t��ng)�M(j��n)�и��N���M(j��n)߀�����M(j��n)һ�����ϵ�y(t��ng)�����ܡ�ԓ��(sh��)���l��Ӌ(j��)���и��١����_���ɿ������ɔ_�ԏ�(qi��ng)�ͬF(xi��n)��(ch��ng)�ɾ��̵ȃ�(y��u)�c(di��n)��

2.2 VHDL�Z(y��)�Խ�BVHDL(Very-high-speed Integrated Circuit Hardware Description Language)�Q����1982�ꡣ1987��ף�VHDL��IEEE��The Institute of Electrical and Electronics Engineers��������(gu��)��(gu��)�����_�J(r��n)���(bi��o)��(zh��n)Ӳ�������Z(y��)�ԡ���IEEE������VHDL�Ę�(bi��o)��(zh��n)�汾��IEEE-1076��֮��EDA��˾���^�Ƴ����Լ���VHDL�O(sh��)Ӌ(j��)�h(hu��n)�����������Լ����O(sh��)Ӌ(j��)���߿��Ժ�VHDL�ӿڡ��˺�VHDL������O(sh��)Ӌ(j��)�I(l��ng)��õ��ˏV���Ľ��ܣ�����ȡ����ԭ�еķǘ�(bi��o)��(zh��n)Ӳ�������Z(y��)�ԡ�1993�꣬IEEE��(du��)VHDL�M(j��n)������ӆ���ĸ��ߵij���Ӵκ�ϵ�y(t��ng)���������ϔU(ku��)չVHDL�ă�(n��i)�ݣ��������°汾��VHDL����IEEE��(bi��o)��(zh��n)��1076-1993�汾���F(xi��n)�ڣ�VHDL��VERILOG����IEEE�Ĺ��I(y��)��(bi��o)��(zh��n)Ӳ�������Z(y��)�ԣ��ֵõ�����EDA��˾��֧�֣�����ӹ����I(l��ng)���ѳɞ���(sh��)�ϵ�ͨ��Ӳ�������Z(y��)�ԡ��Ќ����J(r��n)�飬���µ����o(j��)�У�VHDL��VERILOG�Z(y��)�Ԍ��Г�(d��n)����ȫ���Ĕ�(sh��)��ϵ�y(t��ng)�O(sh��)Ӌ(j��)�΄�(w��)��

2.2.1 VHDL�����c(di��n)VHDL��Ҫ����������(sh��)��ϵ�y(t��ng)�ĽY(ji��)��(g��u)���О顢���ܺͽӿڡ����˺����S�����Ӳ���������Z(y��)���⣬VHDL���Z(y��)����ʽ�������L(f��ng)���Լ��䷨ʮ�������һ���Ӌ(j��)��C(j��)��(j��)�Z(y��)�ԡ�VHDL�ij���Y(ji��)��(g��u)���c(di��n)�nj�һ�(xi��ng)�����O(sh��)Ӌ(j��)����Q���O(sh��)Ӌ(j��)��(sh��)�w��������һ��(g��)Ԫ����һ��(g��)�·ģ�K��һ��(g��)ϵ�y(t��ng)���ֳ��ⲿ���ַQ���ҕ���֣����˿ڣ��̓�(n��i)�����ַQ�鲻��ҕ���֣������O(sh��)Ӌ(j��)��(sh��)�w�ă�(n��i)�����ܺ��㷨��ɲ��֡��ڌ�(du��)һ��(g��)�O(sh��)Ӌ(j��)��(sh��)�w���x���ⲿ�����һ�����(n��i)���_(k��i)�l(f��)��ɺ��������O(sh��)Ӌ(j��)�Ϳ���ֱ���{(di��o)���@��(g��)��(sh��)�w���@�N���O(sh��)Ӌ(j��)��(sh��)�w�ֳɃ�(n��i)�ⲿ�ֵĸ�����VHDLϵ�y(t��ng)�O(sh��)Ӌ(j��)�Ļ����c(di��n)����(y��ng)��VHDL�M(j��n)�й����O(sh��)Ӌ(j��)�ă�(y��u)�c(di��n)�Ƕ��ģ����w���£�

1���c������Ӳ�������Z(y��)����ȣ�VHDL���и���(qi��ng)���О������������Ķ��Q�������ɞ�ϵ�y(t��ng)�O(sh��)Ӌ(j��)�I(l��ng)����ѵ�Ӳ�������Z(y��)�ԡ���(qi��ng)����О����������DZ��_(k��i)���w�������Y(ji��)��(g��u)����߉�О����������O(sh��)Ӌ(j��)��Ҏ(gu��)ģ���ϵ�y(t��ng)����Ҫ���C����Ŀǰ���е�EDA���ߺ�VHDL�C�������ԣ������ڳ�����О������L(f��ng)���VHDL����C�ϳɞ���w��FPGA��CPLD��Ŀ��(bi��o)�����ľW(w��ng)���ļ��Ѳ��Ɇ�(w��n)�}��ֻ���ھC���c��(y��u)��Ч�������в��

2��VHDL���������һ�N�����(bi��o)��(zh��n)��ʽ���F(xi��n)�ģ����VHDL����һ�NӲ���·�������O(sh��)Ӌ(j��)�Z(y��)�ԣ�Ҳ��һ�N��(bi��o)��(zh��n)�ľW(w��ng)����ʽ��߀��һ�N�����Z(y��)�ԡ����S���ķ����Z(y��)��͎�(k��)����(sh��)��ʹ�����κδ�ϵ�y(t��ng)���O(sh��)Ӌ(j��)���ڣ�����δ��ɣ����������ڲ��(y��n)�O(sh��)Ӌ(j��)ϵ�y(t��ng)�Ĺ��ܿ����ԣ��S�r(sh��)�Ɍ�(du��)�O(sh��)Ӌ(j��)�M(j��n)�з���ģ�M�������h(yu��n)�x�T(m��n)��(j��)�ĸߌӴ����M(j��n)��ģ�M��ʹ�O(sh��)Ӌ(j��)�ߌ�(du��)����(g��)�����O(sh��)Ӌ(j��)�ĽY(ji��)��(g��u)���ܵĿ����������Q�ߡ�

3��VHDL�Z(y��)����О����������ͳ���Y(ji��)��(g��u)�Q����������֧�ִ�Ҏ(gu��)ģ�O(sh��)Ӌ(j��)�ķֽ�������O(sh��)Ӌ(j��)�������ù��ܣ������Ј�(ch��ng)������ģ���Ҏ(gu��)ģϵ�y(t��ng)��Ч�����ٵ���ɱ���ɶ�����������(g��)�_(k��i)�l(f��)�M��ͬ���й������܌�(sh��)�F(xi��n)�����c(di��n)��VHDL���O(sh��)Ӌ(j��)��(sh��)�w�ĸ��������ĸ���O(sh��)Ӌ(j��)��(k��)�ĸ�����O(sh��)Ӌ(j��)�ķֽ�Ͳ��й����ṩ��������֧�֡�

4����(du��)����VHDL��ɵ�һ��(g��)�_�����O(sh��)Ӌ(j��)����������EDA�����M(j��n)��߉�C�Ϻ̓�(y��u)�������Ԅ�(d��ng)�ذ�VHDL�����O(sh��)Ӌ(j��)�D(zhu��n)׃�ɞ��T(m��n)��(j��)�W(w��ng)�����@�N��ʽͻ�����T(m��n)��(j��)�·�O(sh��)Ӌ(j��)��ƿ�i���O��p�����·�O(sh��)Ӌ(j��)�ĕr(sh��)�g�Ϳ��ܰl(f��)�����e(cu��)�`���������_(k��i)�l(f��)�ɱ�����(y��ng)��EDA���ߵ�߉��(y��u)�����ܣ������Ԅ�(d��ng)�ذ�һ��(g��)�C�Ϻ���O(sh��)Ӌ(j��)׃��һ��(g��)����Ч�������ٵ��·ϵ�y(t��ng)�����^(gu��)��(l��i)���O(sh��)Ӌ(j��)��߀�������؏ľC�Ϻ̓�(y��u)������·�@���O(sh��)Ӌ(j��)��Ϣ������ȥ������VHDL�O(sh��)Ӌ(j��)������ʹ֮�������ơ�

5��VHDL��(du��)�O(sh��)Ӌ(j��)��������������(du��)��(d��)���ԣ��O(sh��)Ӌ(j��)�߿��Բ���Ӳ���ĽY(ji��)��(g��u)��Ҳ���ع���K�O(sh��)Ӌ(j��)��(sh��)�F(xi��n)��Ŀ��(bi��o)������ʲô�����M(j��n)�Ъ�(d��)�����O(sh��)Ӌ(j��)������?y��n)�VHDLӲ�������c���w�Ĺ�ˇ���g(sh��)��Ӳ���Y(ji��)��(g��u)�o(w��)�P(gu��n)��VHDL�O(sh��)Ӌ(j��)�����Ӳ����(sh��)�F(xi��n)Ŀ��(bi��o)�����ЏV韵��x�������а�����ϵ�е�CPLD��FPGA�����N�T(m��n)��Ќ�(sh��)�F(xi��n)Ŀ��(bi��o)��

6������VHDL����������Z(y��)����ӳ����{(di��o)�õȹ��ܣ���(du��)������ɵ��O(sh��)Ӌ(j��)���ڲ���׃?c��)�����ėl���£�ֻ��Ҫ��׃�˿�م�����(sh��)�������p�ظ�׃?c��)O(sh��)Ӌ(j��)��Ҏ(gu��)ģ�ͽY(ji��)��(g��u)��

2.2.2 ����VHDL����������O(sh��)Ӌ(j��)����2.2.2.1 ��������O(sh��)Ӌ(j��)�����E1���O(sh��)Ӌ(j��)�f(shu��)��������Ȼ�Z(y��)�Ա��_(d��)ϵ�y(t��ng)�(xi��ng)Ŀ�Ĺ������c(di��n)�ͼ��g(sh��)����(sh��)�ȡ�

2������VHDL�О�ģ�ͣ������O(sh��)Ӌ(j��)�f(shu��)�����D(zhu��n)����VHDL�О�ģ�͡�����ģ���Ǟ���ͨ�^(gu��)VHDL��������(du��)����(g��)ϵ�y(t��ng)�M(j��n)��ϵ�y(t��ng)�О����������u(p��ng)����

3��VHDL�О���档�@һ�A�ο�������VHDL��������(du��)플�ϵ�y(t��ng)���О�ģ���M(j��n)�з���y(c��)ԇ���z��ģ�M�Y(ji��)�����^���M(j��n)���ĺ����ơ�

4��VHDL-RTL��(j��)��ģ������VHDL���О�ģ�ͱ��_(d��)��VHDL�О���a��

5��ǰ�˹��ܷ��档����(du��)VHDL-RTL��(j��)ģ���M(j��n)�з��棬��(ji��n)�Q���ܷ��档

6��߉�C�ϡ�ʹ��߉�C�Ϲ��ߌ�VHDL�О���a�����D(zhu��n)����Y(ji��)��(g��u)�����T(m��n)��(j��)�·��

7���y(c��)ԇ�������ɡ�

8�����ܷ��档

9���Y(ji��)��(g��u)�C�ϡ�

10���T(m��n)��(j��)�r(sh��)����档

11��Ӳ���y(c��)ԇ��

2.2.2.2 Top-down�O(sh��)Ӌ(j��)�����ă�(y��u)�c(di��n)1����ȫ�����O(sh��)Ӌ(j��)�ˆT���O(sh��)Ӌ(j��)˼·���Ĺ��������_(k��i)ʼ�����������팍(sh��)�F(xi��n)��

2�������O(sh��)Ӌ(j��)����ȫ��(d��)�������팍(sh��)�F(xi��n)������Top-Down�O(sh��)Ӌ(j��)����������ݔ����Ç�(gu��)�H��(bi��o)��(zh��n)��HDLݔ�뷽����HDL�ɲ������κ�������������Ϣ����˹��̎������и���Ŀ��gȥ���о����M(j��n)�й����������O(sh��)Ӌ(j��)���������O(sh��)Ӌ(j��)�^(gu��)�̵�����A�������x��������������������(hu��)���O(sh��)Ӌ(j��)һ�_(k��i)ʼ���ܵ���K�����������ļs����

3���O(sh��)Ӌ(j��)�������ã��O(sh��)Ӌ(j��)�Y(ji��)����ȫ������һ�N֪�R(sh��)�a(ch��n)��(qu��n)��IP-Intellectual Property���ķ�ʽ�����O(sh��)Ӌ(j��)�����O(sh��)Ӌ(j��)��λ���O(sh��)Ӌ(j��)�ɹ�����(y��ng)���ڲ�ͬ�Įa(ch��n)Ʒ�O(sh��)Ӌ(j��)�У������ɹ��������á�

4�������O(sh��)Ӌ(j��)�ĸ��ģ��O(sh��)Ӌ(j��)���̎����ژO�̵ĕr(sh��)�g��(n��i)���O(sh��)Ӌ(j��)����(du��)���NFPGA/CPLD�Y(ji��)��(g��u)�M(j��n)���O(sh��)Ӌ(j��)�Y(ji��)��Ҏ(gu��)ģ���T(m��n)���ģ����ٶȣ��r(sh��)�ı��^���x���(y��u)������

5���O(sh��)Ӌ(j��)��̎����Ҏ(gu��)ģ��(f��)�s�·��Ŀǰ��FPGA/CPLD����������ɶȡ����ˇ�l(f��)չ�����O(sh��)Ӌ(j��)ϵ�y(t��ng)��С�ͻ������ġ��߿ɿ��Ե��ṩ�˼��ɵ��ֶΡ�

6���O(sh��)Ӌ(j��)���ڿs�̣����a(ch��n)�ʴ����ߣ��a(ch��n)Ʒ���Еr(sh��)�g��ǰ���������@��ߣ��a(ch��n)Ʒ��(j��ng)��(zh��ng)���ӏ�(qi��ng)����(j��)�y(t��ng)Ӌ(j��)������Top-Down�O(sh��)Ӌ(j��)���������a(ch��n)�ʿ��_(d��)�����y(t��ng)�O(sh��)Ӌ(j��)����2��4����

2.3 FPGA�_(k��i)�l(f��)��B2.3.1 FPGA��(ji��n)���F(xi��n)��(ch��ng)�ɾ����T(m��n)��У�FPGA�������ǰ�ʮ������ڳ��F(xi��n)���®a(ch��n)Ʒ�����đ�(y��ng)�ô��ط�����IC���O(sh��)Ӌ(j��)������S����(sh��)�ּ��g(sh��)����V���đ�(y��ng)�ã���FPGA�������ASIC�����õ���Ѹ�ٵ��ռ��Ͱl(f��)չ���������ɶȺ��ٶȶ��ڸ������L(zh��ng)��

���y(t��ng)���·�O(sh��)Ӌ(j��)�^(gu��)���ǣ��Ȯ�(hu��)ԭ��D����ԭ��D�L�Ƴ�ӡ���·��D�����ư桢���b���{(di��o)ԇ������FPGA���҂�ֻ��Ҫ��Ӌ(j��)��C(j��)���L��ԭ��D�����\(y��n)������(y��ng)��ܛ�����Ϳɰ����O(sh��)Ӌ(j��)��߉�·��FPGA�Ќ�(sh��)�F(xi��n)�����в��E�����Ԅ�(d��ng)��ɡ�����O(sh��)Ӌ(j��)���̎��Լ��O(sh��)Ӌ(j��)���ü����·�ɞ���һ�����������顣

FPGA���錣�ü����·��ASIC�������ϵ�һ��(g��)���ͷ������T(m��n)�����߶��`����Ñ��F(xi��n)��(ch��ng)���̷�ʽ���F(xi��n)��(ch��ng)���x��������(sh��)�ֆ�Ƭϵ�y(t��ng)���������܉��؏�(f��)���x������(f��)�Č�(xi��)���·f���ܣ����(f��)�s��(sh��)��ϵ�y(t��ng)�O(sh��)Ӌ(j��)�������Լ��a(ch��n)Ʒ�_(k��i)�l(f��)�ṩ����Ч�ļ��g(sh��)�ֶΡ���ӑ�(y��ng)���O(sh��)Ӌ(j��)���̎���(y��ng)��FPGA���g(sh��)���H�ɱ���ͨ��ASIC��Ƭϵ�y(t��ng)�O(sh��)Ӌ(j��)�����L(zh��ng)��ǰ��Ͷ�Y�L(f��ng)�U(xi��n)������c(di��n)�����ҿ˷����^(gu��)ȥ�弉(j��)ͨ�Ô�(sh��)���·��(y��ng)���O(sh��)Ӌ(j��)��������Ͳ��ɿ��ԡ�

ĿǰFPGA�ăɂ�(g��)��Ҫ�l(f��)չ�cͻ���ǣ������(sh��)�S������߶������϶��ṩ��Ƭ�ϵ�̎��������CPU��DSP����Ӳ�ˣ�Hard Core����̻��ˣ�Fixed Core��������Xilinx��Virtex II ProоƬ�����ṩPower PC����Altera��Stratix��Excalibur��ϵ��оƬ�����ṩNios��DSP��Arm��ģ�K����FPGA�ϼ���̎������ʹSOPC�O(sh��)Ӌ(j��)���ӱ����c��(qi��ng)����һ��(g��)�l(f��)չ���ڲ�ͬ�������Ƴ��ĸ߶�оƬ�ϴ����˸��ٴ����հl(f��)����һ���܉��_(d��)��3Gb/s���ϵĔ�(sh��)��(j��)̎����������Xilinx��Altera��Lattice��������(y��ng)��������̖(h��o)�ṩԓ���ܡ��@Щ�¹���ʹFPGA�Ĕ�(sh��)��(j��)�����������������(qi��ng)��

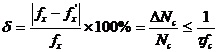

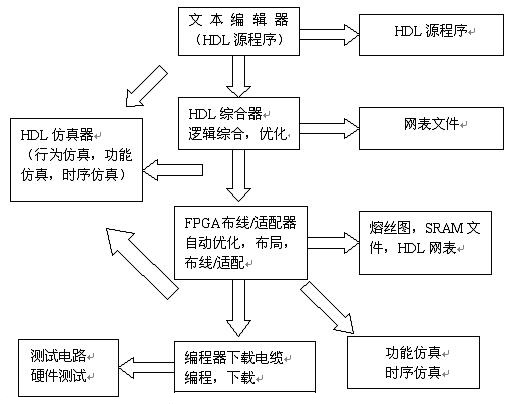

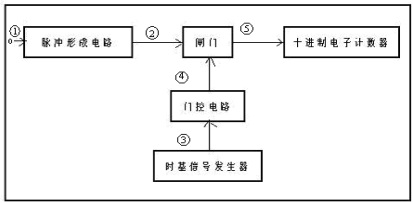

2.3.2 FPGA�O(sh��)Ӌ(j��)������(du��)��Ŀ��(bi��o)������FPGA��CPLD��HDL�O(sh��)Ӌ(j��)���乤���O(sh��)Ӌ(j��)�Ļ���������D 2-1��ʾ���F(xi��n)���w�f(shu��)�����¡�

�D 2-1 EDA�O(sh��)Ӌ(j��)����

1���ı���

���κ��ı������������M(j��n)�У�ͨ��VHDL�ļ������vhd�ļ���Verilog�ļ������v�ļ���

2��ʹ�þ��g���߾��gԴ�ļ�

HDL�ľ��g���кܶ࣬ACTIVE��˾��MODELSIM��˾��SYNPLICITY��˾��SYNOPSYS��˾��VERIBEST��˾�ȶ����Լ��ľ��g����

3��߉�C��

��Դ�ļ��{(di��o)��߉�C��ܛ���M(j��n)�оC�ϡ��C�ϵ�Ŀ�������ڌ��O(sh��)Ӌ(j��)��Դ�ļ����Z(y��)���D(zhu��n)�Q�錍(sh��)�H���·�����Ǵ˕r(sh��)߀�](m��i)����оƬ���γ��������·���@һ������KĿ���������T(m��n)�·��(j��)�ľW(w��ng)��(Netlist)��

4�����֡�����

����3�����ɵľW(w��ng)���ļ��{(di��o)��PLD�S���ṩ��ܛ�����M(j��n)�в����������O(sh��)Ӌ(j��)�õ�߉���ŵ�CPLD��FPGA��(n��i)���@һ����Ŀ���������������d(����Programming)�ľ����ļ������@һ�������õ���3�����ɵľW(w��ng)����������(j��)CPLD��FPGA�S�̵������������Y(ji��)��(g��u)���M(j��n)�в��֡��������@�ͺ������O(sh��)Ӌ(j��)PCB�r(sh��)�IJ��ֲ���һ�ӡ��Ȍ�����(g��)�O(sh��)Ӌ(j��)�е��T(m��n)����(j��)�W(w��ng)���ă�(n��i)�ݺ������ĽY(ji��)��(g��u)�����������ض���λ��Ȼ���ڸ���(j��)�W(w��ng)�����ṩ�ĸ��T(m��n)���B�ӣ��Ѹ���(g��)�T(m��n)��ݔ��ݔ���B������(l��i)���������һ��(g��)�����̵��ļ����@һ��ͬ�r(sh��)߀��(hu��)��һЩ�r(sh��)����Ϣ(Timing)������O(sh��)Ӌ(j��)�(xi��ng)Ŀ��ȥ���Ա�����������档

5�������

�����ڲ��ֲ����Ы@�õľ��_����(sh��)���÷���ܛ���(y��n)�C�·�ĕr(sh��)��(Ҳ�в��ֲ��������r(sh��)�����)���@һ����Ҫ�Ǟ��˴_������O(sh��)Ӌ(j��)�ڽ�(j��ng)�^(gu��)���ֲ���֮���Dz���߀�M������O(sh��)Ӌ(j��)Ҫ��

6�����̣����d

���ǰ�ײ����](m��i)�аl(f��)���e(cu��)�`�����ҷ����O(sh��)Ӌ(j��)Ҫ���@һ���Ϳ��Ԍ����m�����Ȯa(ch��n)�������û����d�ļ�ͨ�^(gu��)�����������d��|���d��Ŀ��(bi��o)оƬ�С�

7��Ӳ���y(c��)ԇ

Ӳ���y(c��)ԇ��Ŀ���Ǟ����ڸ��挍(sh��)�ĭh(hu��n)���Йz�(y��n)HDL�O(sh��)Ӌ(j��)���\(y��n)����r���e�nj�(du��)��HDL�����O(sh��)Ӌ(j��)�ϲ���ʮ��Ҏ(gu��)�����Z(y��)�x�Ϻ���һ�����x�ij���

2.3.3 SPARTAN-IIоƬ��(ji��n)�����O(sh��)Ӌ(j��)�õ���FPGAоƬ��XILINX��˾���a(ch��n)��SPARNTAN-IIϵ���е�xc2s100-6�����挢��(du��)ԓϵ������(ji��n)�εĽ�B��

2.3.3.1 Spartan-IIϵ�е����c(di��n)�M(j��n)��ASSP���I(l��ng)��FPGA���ژO����ASSP���·���ϔD��ȥ,��ʹ��ʧȥ�O(sh��)Ӌ(j��)�ˆT�Č���(��i)�������κ��fʽ��FPGA�������o(w��)��ǡ��(d��ng)?sh��)��������������ֻ��Spartan-II FPGA���������@һ�c(di��n)��Spartan-IIϵ�О��O(sh��)Ӌ(j��)�ˆT�ṩ�������ķ��b�����ܶȡ����ܺ������Լ��\(y��n)���ٶȷ��涼��ࡣ���ǣ�Spartan-II���Q�������ṩ�Ŀɾ�������������ăr(ji��)ֵ���Ķ�ʹ���cASSP/ASIC������Ⱦ����˺ܴ�ă�(y��u)��(sh��)��

1���F(xi��n)��(ch��ng)����(j��)���`����

Spartan-II FPGA�Ŀɾ����������O(sh��)Ӌ(j��)�ˆT����(l��i)�ܴ�(y��u)��(sh��)�����õ�FPGA�ǘ�(bi��o)��(zh��n)���������ɸ���،��a(ch��n)Ʒ��(bi��o)��(zh��n)������?y��n)�Spartan�������M(j��n)�ЬF(xi��n)��(ch��ng)����(j��)������(j��)�������dܛ��һ�Ӻ�(ji��n)�Ρ�

2�������S����߉�T(m��n)�YԴ

Spartan-IIϵ���������������ܶȸ��_(d��)20�f(w��n)�T(m��n)���S����߉�T(m��n)�YԴ���O(sh��)Ӌ(j��)�߸����ȵİl(f��)�]��

3����eASIC��FPGA�g�����ܺ��ܲ��

�����ܺ��ܷ��棬�����(sh��)�O(sh��)Ӌ(j��)�ˆT����(hu��)�뵽ASIC��FPGA�g�ľ��ࡣ����SPARTAN-II�������@һ��ࡣ

4���������Ĵ惦(ch��)��

Ƭ�ώ��惦(ch��)���DZ�횵ģ����߀���кܺõ��`���Ե�Ԓ����ô���������ˡ��ֲ�ʽ�惦(ch��)���͉KRAM�ɸ�Ч�،�(sh��)�F(xi��n)���m����Ҫ������ã��F(xi��n)�r(sh��)߀�ɲ����cƬ�ϴ惦(ch��)��һ�ӿ���ⲿ�惦(ch��)����

5������ĕr(sh��)犹���

��������R�r(sh��)犹��톖(w��n)�}��Spartan-IIϵ�е��Ă�(g��)�߶��`���DLL�ɽ�Q���Ć�(w��n)�}���O(sh��)Ӌ(j��)�ˆT����Ƭ�ό�(du��)ݔ��r(sh��)��M(j��n)�б��l����l��߀���(q��)��(d��ng)���ϵĶ���(g��)�r(sh��)犡�

6���ṩ������

����Ĕ�(sh��)�����������S���µ�I/O��(bi��o)��(zh��n)Ҫ��ܿ��̡�ͨ�^(gu��)Select I/O���g(sh��)��Spartan-II����֧�������@Щ��I/O��(bi��o)��(zh��n)��I/O�ٶȳ��^(gu��)200 MHz��Spartan-IIϵ���S���Ĺ��ܡ��Լ������ܺ͵ͳɱ���ʹ��ɞ��N��(sh��)��(j��)�W(w��ng)�j(lu��)��(y��ng)��HDLC��������Q�����е����x��Spartan-IIҲ�dz��m�ڌ�(sh��)�F(xi��n)���ƺͽӿ�߉���������ڌ�CPUͬQDR SRAM�B����һ��

7�������ܶȔU(ku��)չ��20�f(w��n)�T(m��n)

�S�������a(ch��n)Ʒ���O(sh��)Ӌ(j��)׃��Խ��(l��i)Խ��(f��)�s����(du��)�����ܶȡ�����惦(ch��)���YԴ�Լ�����I/O��(sh��)��������Ҳ�����L(zh��ng)����(du��)�ڴ���O(sh��)Ӌ(j��)��Spartan-IIϵ�е�XC2S200�dz��m�ϣ�ԓ�������ṩ20���f(w��n)��(g��)�T(m��n)��14��(g��)RAM�K�Լ�284��(g��)I/O���������N��ͬ�ĵͳɱ��m�ϴ��������a(ch��n)�ķ��bPQ208��FG256��FG456�ɹ��x������XC2S200���ɫ@�ñ�XC2S150��36%��߉��Ԫ���������ܶ���Spartan��Spartan-XL��������ܶȵ��屶��XC2S200������֧��Spartan-II��Q�����@�óɹ����������ԡ�

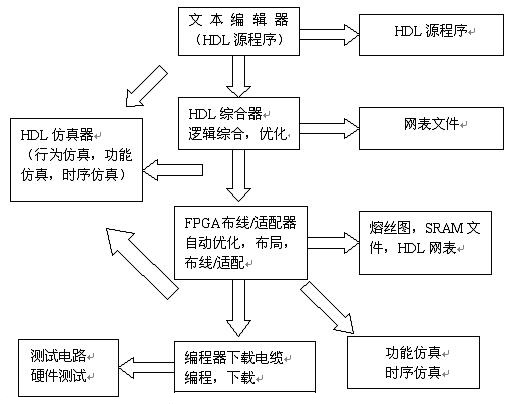

2.3.3.2 Spartan-II�ĽY(ji��)��(g��u)���c(di��n)1���Y(ji��)��(g��u)��D

Spartan-IIϵ��FPGA�����˳�Ҏ(gu��)���`��ɾ��̘�(g��u)�ܣ�����������߉�K��CLB���ͭh(hu��n)�@��CLB���ܵĿɾ���ݔ��/ݔ��ģ�K��IOB������ͨ�^(gu��)����;�����YԴ�γɏ�(qi��ng)��Ļ��B�wϵ��

�D2-2 Spartan-ii �ĽY(ji��)��(g��u)��D

2��ݔ��/ݔ��ģ�K

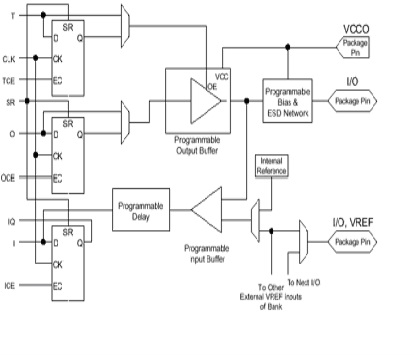

Spartan-II��IOB��ݔ���ݔ��֧��16�NI/O��̖(h��o)��(bi��o)��(zh��n)������LVCMOS��HSTL��SSTL��GTL���@Щ����ݔ���ݔ����֧�ָ��N���M(j��n)�Ĵ惦(ch��)���Ϳ����ӿڡ�����(g��)IOB�Ĵ���������߅���|�l(f��)D���|�l(f��)���������ƽ���е��i������

�D2-3 Spartan-ii ��ݔ��ݔ��ģ�K

3��߉��Ԫ

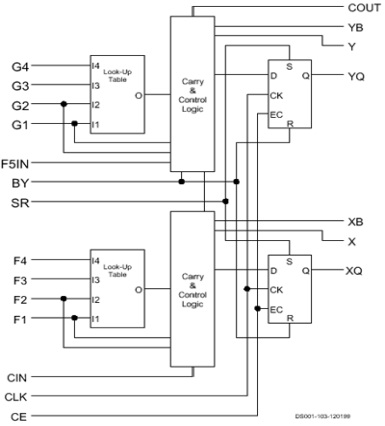

Spartan-II CLB�Ļ�����(g��u)���Ԫ��߉��Ԫ��LC����һ��(g��)LC����һ��(g��)��ݔ��ĺ���(sh��)�l(f��)������һ��(g��)�M(j��n)λ߉��һ��(g��)�惦(ch��)��Ԫ��ÿ��(g��)LC�к���(sh��)�l(f��)������ݔ��ͬ�r(sh��)�(q��)��(d��ng)CLBݔ���˺��|�l(f��)����Dݔ��ˡ�ÿ��(g��)Spartan-II CLB�����Ă�(g��)LC���ɃɽM�ϳɃɂ�(g��)ͬ�ӵ�Slice�������Ă�(g��)����LC�⣬Spartan-II CLB߀����һЩ߉�·���Y(ji��)�Ϻ���(sh��)�l(f��)�������ṩ�傀(g��)������(g��)ݔ��ĺ���(sh��)���ܡ���ˮ�(d��ng)�A(y��)Ӌ(j��)�o�����������ṩ��ϵ�y(t��ng)�T(m��n)��(sh��)���r(sh��)��ÿ��(g��)CLB�ɮ�(d��ng)��4.5��(g��)߉��Ԫ��(l��i)Ӌ(j��)�㡣

Spartan-II����(sh��)�l(f��)��������4ݔ����ұ���LUT���ķ�ʽ��(l��i)��(sh��)�F(xi��n)���������麯��(sh��)�l(f��)�������⣬ÿ��(g��)LUT߀������һ��(g��)16*1λ��ͬ��RAM��(l��i)ʹ�á�Spartan-II LUT߀������һ��(g��)16λ��λ�Ĵ���ʹ�ã����Ҍ�(du��)�ڲ����ٻ�⧰l(f��)��(sh��)��(j��)�dz����롣�@һģʽ߀�����T�电(sh��)����̖(h��o)̎���ȑ�(y��ng)�������ڔ�(sh��)��(j��)�Ĵ惦(ch��)��Spartan-II߉Ƭ�еĴ惦(ch��)��Ԫ��ͨ�^(gu��)���óɞ�߅���|�l(f��)��D���|�l(f��)�����ƽ�����i������

�D2-4 Spartan-ii��߉��Ԫ

4.�KRAM

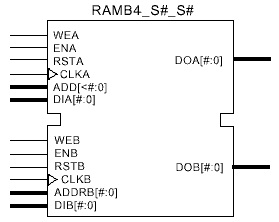

Spartan-II FPGA�����ˎK���͵�4Kλ����Select RAM+ �惦(ch��)���K���@�c��CLB���܉�?q��)��F(xi��n)�\RAM�Y(ji��)��(g��u)�ķֲ�ʽSelect RAM+�YԴ�����a(b��)�䡣ÿ��(g��)�惦(ch��)���K�����Þ�4K x 1 ��256 x 16֮�g�Ķ�N��ͬ���á�

�D2-5 Spartan-ii�ĉKRAM

5.���t�i��h(hu��n)

�cÿ��(g��)ȫ�֕r(sh��)�ݔ�뾏�_�����B����һ��(g��)��ȫ��(sh��)�ֵ����t�i��h(hu��n)��DLL�������������r(sh��)�ݔ�뺸�P(p��n)��������(n��i)���r(sh��)�ݔ�����_�g�Ļ�׃��ÿ��(g��)DLL���(q��)��(d��ng)�ɂ�(g��)ȫ�֕r(sh��)犾W(w��ng)�j(lu��)�����ȱO(ji��n)ҕݔ��ĕr(sh��)���̖(h��o)��Ȼ���Ƿֲ�ʽ�r(sh��)���̖(h��o)�����Ԅ�(d��ng)���{(di��o)���r(sh��)����t��Ԫ��ͨ�^(gu��)�����~������t��(l��i)���C�r(sh��)�߅�؇�(y��n)����ڵ��_(d��)�r(sh��)�ݔ���һ��(g��)�r(sh��)����ں��_(d��)��(n��i)���|�l(f��)����ͨ�^(gu��)���C���_(d��)��(n��i)���|�l(f��)���ĕr(sh��)�߅���c���_(d��)�r(sh��)�ݔ��˵ĕr(sh��)�߅�؇�(y��n)��ͬ�����@һ�]�h(hu��n)ϵ�y(t��ng)��Ч�������˕r(sh��)犂�ݔ���t��

������ ��(sh��)���l��Ӌ(j��)��ܛ���_(k��i)�l(f��)�h(hu��n)��������Ҫ��B�(xi��ng)Ŀ�Ќ�Ҫ�õ���һϵ��ܛ������������VHDL�Z(y��)�Ծ���(xi��)�;��g��ISEܛ�������ڳ������ķ���ܛ��ModelSim��

3.1 �_(k��i)�l(f��)�h(hu��n)���S���ɾ�������������Խ���f(w��n)�T(m��n)��(j��)���O(sh��)Ӌ(j��)�����R�Įa(ch��n)Ʒ�����c�O(sh��)Ӌ(j��)Ч�ʵ�����(zh��n)ҲԽ��(l��i)Խ���O(sh��)Ӌ(j��)�߱�횺����x���EDA�S���ṩ�ļ����O(sh��)Ӌ(j��)�Ĺ���ܛ�����@�Ӳ������^�̵ĕr(sh��)�g��(n��i)�O(sh��)Ӌ(j��)����Ч��(w��n)���Įa(ch��n)Ʒ���ڱ����O(sh��)Ӌ(j��)�У������x���FPGAоƬ����Xilinx��˾���a(ch��n)�ģ������҂���Ҫʹ��ModelSim��ISEܛ���M(j��n)�з���;C�ϡ�

3.2 ModelSim��BModelSim֧��PC��UNIXƽ�_(t��i)���dž�һ��(n��i)��֧��VHDL��Verilog��Ϸ����HDL�Z(y��)�Է�������ModelSim���H��������O(sh��)Ӌ(j��)�Ĺ����(y��n)�C��Ҳ�Ɍ�(sh��)�F(xi��n)߉�C�Ϻ���T(m��n)��(j��)�����Լ����ֲ�����Ĺ����c�r(sh��)���(y��n)�C��

ModelSim��ȫ֧��VHDL��Verilog��(bi��o)��(zh��n)������ֱ�Ӿ����g(sh��)��������HDL���g�ͷ����ٶȡ�߀��������ModelSim�{(di��o)���O(sh��)Ӌ(j��)�ļ��M(j��n)�з�����������{(di��o)ԇ�h(hu��n)���У��O(sh��)Ӌ(j��)�߿���ͨ�^(gu��)ModelSim�Ŀ����{(di��o)ԇ���E�Լ���(du��)���N��̖(h��o)�ıO(ji��n)�ع��ܣ��o(w��)Փ��̖(h��o)̎��VHDL�ӣ�߀��̎�ڻ���Z(y��)�Ԍӣ�ʹ����Ĉ�(zh��)���^(gu��)������ֱ�^���������O(sh��)Ӌ(j��)���r(sh��)�l(f��)�F(xi��n)©�����s���O(sh��)Ӌ(j��)���ڡ�

ModelSim�������c(di��n)���䏊(qi��ng)����{(di��o)ԇ���ܣ����M(j��n)�Ĕ�(sh��)��(j��)�����ڣ�����Ѹ��ۙ�����a(ch��n)���������e(cu��)�`��B(t��i)��ԭ�����ܷ������ߎ�����������ƿ�i�����ٷ��棻���a���w�ʙz��_���y(c��)ԇ����䣻��Nģʽ�IJ��α��^���ܣ����M(j��n)�� SignalSpy���ܣ����Է�����L��(w��n)VHDL����VHDL��Verilog����O(sh��)Ӌ(j��)�еĵ���̖(h��o)��֧�ּ���IP�����Ԍ�(sh��)�F(xi��n)�cMatlab��Simulink��(li��n)�Ϸ��档

3.2.1 ISE�h(hu��n)����ModelSim��ʹ��ModelSim��һ��(g��)��(d��)���ķ��湤�ߣ����ڹ����ĕr(sh��)����Ҫ����ܛ���ąf(xi��)������Xilinx��˾��ISE�����_(k��i)�l(f��)�h(hu��n)���нoModelSim����ܛ���A(y��)���˽ӿڣ�ͨ�^(gu��)�@��(g��)�ӿڿ��ԏ�ISE���ɭh(hu��n)����ֱ�ӆ���(d��ng)ModelSim�����M(j��n)�з��档�@��(g��)�^(gu��)��ͨ����(hu��)�o���W(xu��)��һ��(g��)�e(cu��)�X(ju��)���Ԟ�ISE���ɭh(hu��n)����ModelSim������(li��n)�Ϲ����ģ��䌍(sh��)ISE���](m��i)�м���ModelSim���ߣ�ֻ���A(y��)����ܛ���ӿڡ������f(shu��)��ModelSim���Ñ��ӿڣ���ʹ�Ï�ISE�����_(k��i)�l(f��)�h(hu��n)����ֱ�ӆ���(d��ng)ModelSim���湤�ߵķ�����ʹ�ô˷N��������(d��ng)ModelSim������Ҫ�߂�3��(g��)�l������һ������(d��ng)ISE�����_(k��i)�l(f��)�h(hu��n)����������һ��(g��)FPGA��CPLD�Ĺ����(xi��ng)Ŀ���ڶ��������O(sh��)Ӌ(j��)Դ���a���Ҿ��gͨ�^(gu��)��������ʹ��ISE�е�TestFixture����TestBenchWaveform���ߞ鮔(d��ng)ǰ���O(sh��)Ӌ(j��)�ṩһ��(g��)�y(c��)ԇģ��(Testbench)�������ڜy(c��)ԇģ���������O(sh��)Ӌ(j��)����(l��)��ֻ�������l���߂�֮��ſ��ԏ�ISE�Į�(d��ng)ǰ�YԴ��������ֱ�ӆ���(d��ng)ModelSim���߲��\(y��n)�з��棬����ʹ��ISE�Ԏ���һ��(g��)���Ӽ����f(shu��)����

��ISE��ֱ�ӆ���(d��ng)ModelSim

1����Windows����ϵ�y(t��ng)���x��[�_(k��i)ʼ]��[����]��[Xilinx ISE 6]��[Project Navigator]�������(d��ng)ISE�����_(k��i)�l(f��)�h(hu��n)����

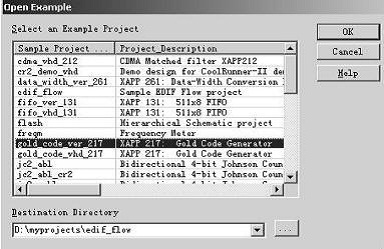

2����ISE���������x��[File]��[Open Example]�������[Open Example]��(du��)Ԓ����D��ʾ��Ȼ����[Select an Example Project]��Ŀ���x��goldcode-ver-217������[Destination Directory]���x���(xi��ng)Ŀ��ŵ�Ŀ䛣��Γ�OK���o���_(k��i)���ӳ���

�D3-1 ���_(k��i)���ӳ���

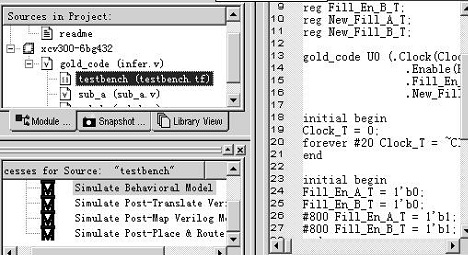

3�����YԴ�������ڣ�Source in Project���е�ģ�Kҕ�D��Model View�����x�еĜy(c��)ԇ�ļ���testbench.tf����������(y��ng)�Į�(d��ng)ǰ�YԴ�������ڣ�Process for Current Source���Ќ���(hu��)���F(xi��n)�cModelsim���������P(gu��n)���О���棨Simulate Behavioral Verilog Model�������g�����(Simulate Post-Map Verilog Model)�Ͳ��ֲ�������棨Simulate Post-Place & Route Verilog Model����4��(g��)��ͬ�IJ����x�(xi��ng)����D��ʾ��

�D 3-2 Modelsim ����

4���p��[Simulate Behavioral Model]�����x�(xi��ng)��������(d��ng)Modelsim��������

5����Modelsim���������x��[View]/[All]������@ʾ���еĴ��ڡ�

�ڮ�(d��ng)ǰ�YԴ�����������x������һ��(g��)�����x�(xi��ng)�����Ԇ���(d��ng)����(y��ng)�A�εķ���������������(y��ng)�A�εķ����ļ������ڣ���ô���ɭh(hu��n)�����Ԅ�(d��ng)���ɷ����ļ������磬��(d��ng)�p���YԴ���������е�[Simulate Post-Place & Route Verilog Model]�����x�(xi��ng)�r(sh��)������(d��ng)�r(sh��)����棬���@һ�����^(gu��)������Ҫ�IJ��ֲ���������ļ��Լ��r(sh��)���(bi��o)ע�ļ���߀�](m��i)�Юa(ch��n)������ôISE�����_(k��i)�l(f��)�h(hu��n)�����Ԅ�(d��ng)�_(k��i)ʼ��(du��)�@��(g��)�����M(j��n)�о��g���C�ϣ����g��ӳ��Ͳ��ֲ����Ȳ������õ����ֲ���������ļ��Լ��r(sh��)���(bi��o)ע�ļ���Ȼ���ن���(d��ng)ModelSim�������M(j��n)�Еr(sh��)����档

3.3 ISE��B����(ji��)��Ҫ��B��XILINX��ISE����ܛ���h(hu��n)���У������VHDL��ԭ��D�ķ�ʽ�M(j��n)���O(sh��)Ӌ(j��)ݔ�룬�����ModelSim���湤�ߌ�(du��)�O(sh��)Ӌ(j��)�M(j��n)�й��ܷ���͕r(sh��)����棬��Ό�(sh��)�F(xi��n)�O(sh��)Ӌ(j��)��

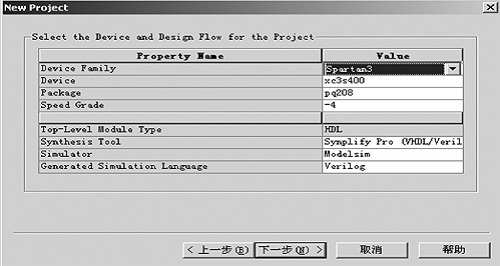

3.3.1 �����(xi��ng)Ŀ���������µ��(xi��ng)Ŀ���̣��x��File�������x��New Project������D�Ϳ����ˡ�

�D 3-3 ISE�����¹���

�x��ʹ�õĿɾ����������device family-��������device-������̖(h��o)package�����bspeed grade-�ٶ�top-level module type-플��ļ����synthesis tool-�C�Ϲ���simulator-���湤��generated simulation language�����ɵķ���ģ���Z(y��)�ԡ�

�D 3-4 �x������

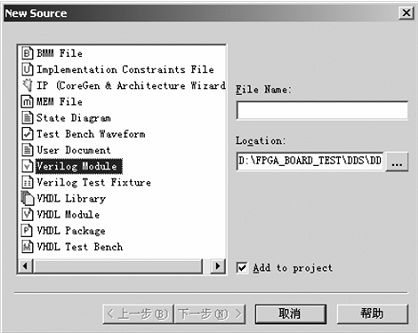

Ȼ��һ·NEXT������c(di��n)����ɡ������ɵĹ����Ǜ](m��i)����͵ģ���Ҫ�Լ����롣�������� sources in project���ғ����x��add sources���x���㌑(xi��)���ļ����뼴�ɡ����Ҫ��(xi��)������ͬ�ӵķ���,�x��new sources���ɣ���(hu��)��������(du��)Ԓ�����x��New Sources����͡�

�D 3-5 �x��New Sources�����

�x��vhdl module����(xi��)���ļ���������һ�(y��)���Ԍ�(xi��)��ݔ��ݔ���ڣ�Ҳ���Բ���(xi��)��һ·NEXT����ɾͿ��ԡ��@�ӾͿ����_(k��i)ʼ��(xi��)���a���^�m(x��)��һ���C���ˡ�Ҫ���_(k��i)���½����ļ���ֱ����sources in project�������p��ԓ�ļ����ɡ�

3.3.2 �О����1���ڹ����(xi��ng)����Project Window��Դ�ļ����x��Ӌ(j��)��(sh��)��(counter.vhd)��

2���x��Project/New Source��

3�����µČ�(du��)Ԓ�����x�����ļ���͞�T(m��n)est Bench Waveform��

4���I���ļ�����counter_tbw��

5���c(di��n)��Next�������������(xi��ng)������Ԍ����testbench�����c����Դ�ļ��P(gu��n)(li��n)��

6��һֱNextֱ��Finish���˕r(sh��)HDL Bencher �����Ԅ�(d��ng)����(d��ng)���Ⱥ���ݔ������ĕr(sh��)��������F(xi��n)�ڿ���ָ����������ĕr(sh��)�g����(sh��)���r(sh��)犸��ƽ�r(sh��)�g�͕r(sh��)犵��ƽ�r(sh��)�gһ���x���O(sh��)Ӌ(j��)��������_(d��)���ĕr(sh��)����ڣ�ݔ�뽨���r(sh��)�g���x��ݔ����ʲô�r(sh��)������Ч��ݔ����Ч�ӕr(sh��)�����x����Ч�r(sh��)��ص��_(d��)���ñ��ݔ����Ч��(sh��)��(j��)��

Ĭ�J(r��n)�ij�ʼ���r(sh��)�g�O(sh��)�����£�

�r(sh��)犸��ƽ�r(sh��)�g: Clock high time: 50 ns ��

�r(sh��)犵��ƽ�r(sh��)�g: Clock low time: 50 ns ��

ݔ�뽨���r(sh��)�g: Input setup time: 10 ns ��

ݔ����Ч�r(sh��)�g: Output valid delay: 10 ns ��

7���c(di��n)��OK������Ĭ�J(r��n)�ĕr(sh��)�g�O(sh��)����Testbench waveform�������¡�

�D 3-6 Testbench Waveform

��HDL Bencher �IJ�����,��ʼ��Ӌ(j��)��(sh��)��ݔ�����£�

��ÿ��(g��)��Ԫ���{(l��n)ɫ�^(q��)��ݔ�뼤��(l��)��

a����CLK��1�������c(di��n)��RESET��Ԫֱ��ԓ��Ԫ׃?y��u)�?/font>

b����CLK��2�������c(di��n)��RESET��Ԫֱ��ԓ��Ԫ׃?y��u)�͡?/font>

c����CLK��3�������c(di��n)��CE��Ԫֱ��ԓ��Ԫ׃?y��u)�ߡ?/font>

d����CLK��2�������c(di��n)��DIR��Ԫֱ��ԓ��Ԫ׃?y��u)�ߡ?/font>

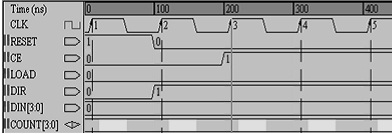

�D 3-7 ����(l��)ݔ��

e�������testbench�ļ���P(p��n)���x��File/Save Waveform���c(di��n)�����ߙڵĴ�P(p��n)�D��(bi��o)������(l��i)HDL Bencher��(hu��)��ʾ���O(sh��)����ϣ������ĕr(sh��)����ڔ�(sh��)��

f����End the testbench __ cycles after the last input assignment��(du��)Ԓ����ݔ��8��Ĭ�J(r��n)ֵ��1��

g���c(di��n)��OK.�˳�HDL Bencher�µ�testbench����Դ�ļ�counter_tbw.tbw�Ԅ�(d��ng)���뵽ԓ�����(xi��ng)�С�

8�������A(y��)�ڵ�ݔ��푑�(y��ng)��

�҂��M(j��n)���О�������(y��n)�CӋ(j��)��(sh��)��ģ�K�Ĺ��ܡ�

a����Sources in Project�������x��counter_tbw.tbw�ļ���

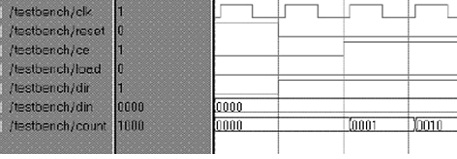

b����Processes for Current Source�������c(di��n)�� + ��̖(h��o)չ�_(k��i)ModelSim�������ČӴνY(ji��)��(g��u)�ҵ����p��Simulate Behavioral VHDL Model���˕r(sh��)ModelSim�������Ԅ�(d��ng)����(d��ng)��

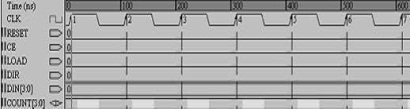

c����(du��)�ڵ�һ���\(y��n)��ModelSim���Ñ���(hu��)�@ʾһ��(g��)��(du��)Ԓ����Ҫ������������̎�����x��Do not show this dialog again�x�(xi��ng)���c(di��n)��Run ModelSim�ˌ�(du��)Ԓ���������°��b����������ModelSim֮ǰ�������@ʾ��ķ���Y(ji��)���F(xi��n)���@ʾ��ModelSim�IJ��δ���(wave window)��

d���c(di��n)��Zoom / Zoom Full���c(di��n)��Zoom / Zoom in��

e���τ�(d��ng)���δ����¶˵ĝL��(d��ng)�l�����ڵ�����ˡ�

�D 3-8 ����D

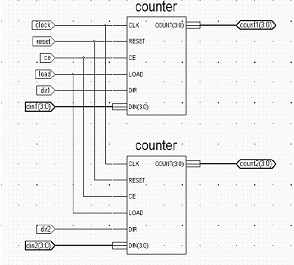

3.3.3 ����플�ԭ��D3.3.3.1 ����ԭ��D��̖(h��o)1����Sources in Project�������x��Ӌ(j��)��(sh��)��ģ�Kcounter.vhd��

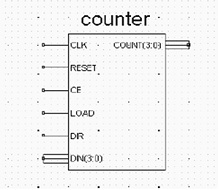

2����Processes for Current Source�����У��c(di��n)���O(sh��)Ӌ(j��)ݔ�댍(sh��)�ó���(Design Entry Utilities)֮ǰ�ġ�+����̖(h��o)Ȼ���p��(chu��ng)��ԭ��D��̖(h��o)(CreateSchematic Symbol)��(j��ng)�^(gu��)���ϲ��E�����Q�顰counter���ĈD�λ�Ԫ�������뵽�����(xi��ng)��(k��)�С�

3.3.3.2 ��(chu��ng)��플�ԭ��D1���ڹ����(xi��ng)��(d��o)����(Project Navigator)�ˆ��У��x��Project/New Source��

2���x��ԭ��D(Schematic)��Դ��͡�

3��ݔ��ԭ��D���顰top����

4�����c(di��n)����Next�����c(di��n)����Finish�����˕r(sh��)ԭ��D����(ECS)�Ԅ�(d��ng)����(d��ng)������ԭ��D�����д��_(k��i)һ����?q��ng)D��

3.3.3.3 ����VHDLģ�K1���ڲˆ����x��Add / Symbol�����ڹ��ߙ����c(di��n)��(Add Symbol)�D��(bi��o)��

2����Ԫ����̖(h��o)�б�(����Ļ�҂�(c��))���x��Ӌ(j��)��(sh��)��counter��ע�ⲻҪ��e(Categories)���������κ��x��

3���c(di��n)�����I�Ɍ�Ӌ(j��)��(sh��)��counter�����ڹ��(bi��o)���ڵ�λ�ó��F(xi��n)��

4����ESC�I�˳����ӷ�̖(h��o)(Add Symbol)ģʽ��

�D 3-9 ����VHDLģ�K

3.3.3.4 ԭ��D�B��1�����ȼ��������ͨ�^(gu��)�ڲˆ����x��Add/Wire�����ڹ��ߙ����c(di��n)�� (Add Wire)�D��(bi��o)��

2������һ���ҿվ�����չ�B������Ӌ(j��)��(sh��)��ģ�K��ijһ���_�Γ����(bi��o)��Ȼ���B�����쵽��Ҫ���L(zh��ng)�ȡ������B�����c(di��n)̎�p�����(bi��o)���oӋ(j��)��(sh��)��ģ�K��ÿһ���_�����B����

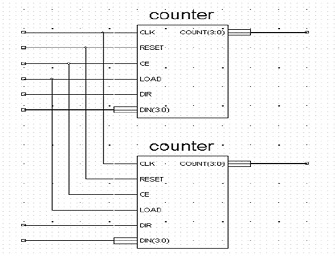

3�����Ӄɂ�(g��)Ԫ����̖(h��o)֮�g���B������һ��(g��)Ӌ(j��)��(sh��)��ģ�K�Ĺ��_̎�Γ����(bi��o)������һ��(g��)Ӌ(j��)��(sh��)��ģ�K�Č�(du��)��(y��ng)���_̎�p�����(bi��o)���B�Ӻþ���ESC�I�˳������B��(Add/Wire)ģʽ��

�D 3-10 ԭ��D�B��

3.3.3.5 ����ݔ��ݔ�����_��(bi��o)ӛ1���ڲˆ����x��Add/ (I/O Marker)���ڹ��ߙ����c(di��n)��(Add I/O Marker)�D��(bi��o)���B�ӺõĈD���¡�

�D 3-11 ����ݔ��ݔ�����_

2���B�Ӳ��E�����Ȟ�clock��reset��ce��load��dir1��dir2����ݔ���(bi��o)ӛ��ͬ�r(sh��)�鿂��din1(3:0)��din2(3:0)����ݔ���(bi��o)ӛ���ڹ��ߙ���߅�ą���(sh��)���x�����x��ݔ��(Input)�������(bi��o)�Ƅ�(d��ng)��ݔ����̖(h��o)���Ķ��c(di��n)���˕r(sh��)���(bi��o)̎�@ʾ��ݔ���(bi��o)ӛ�ĈD�Σ��c(di��n)�����(bi��o)���I��ݔ���(bi��o)ӛ��(hu��)���W(w��ng)�j(lu��)�����������ژ�(bi��o)ӛ�D�εă�(n��i)����

3�������²��E��count���������p����̖(h��o)��(bi��o)ӛ���ڹ��ߙ���߅�ą���(sh��)���x�����x���p��(Bidirectional)�������(bi��o)�Ƅ�(d��ng)��ݔ����̖(h��o)���Ķ��c(di��n)���˕r(sh��)���(bi��o)̎�@ʾ���p����̖(h��o)��(bi��o)ӛ�ĈD�Σ��c(di��n)�����(bi��o)���I��

4���ڲˆ����x��File/Save������ԭ��D,�˳�ԭ��D����(ECS)��

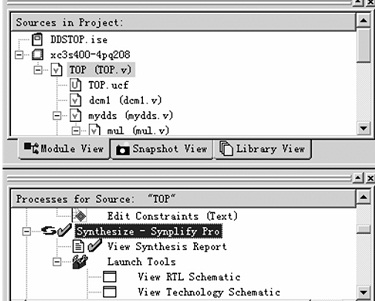

3.3.4 �C��3.3.4.1 Synthesize�C����(d��ng)�㾎��(xi��)�������플�ԭ��D�B�Ӻ��ԺͿ��ԾC���ˡ��x�����플��ļ����p��Synthesize-Synplify Pro��

�D 3-12 �C��

������F(xi��n)�ψD��С������ʾ�C�ϛ](m��i)�І�(w��n)�}��������p��View RTL Schematic��(l��i)�鿴�C�Ϻ��RTLԭ��D��

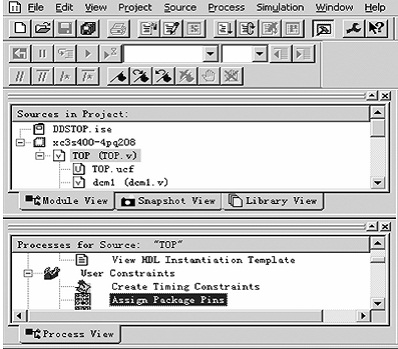

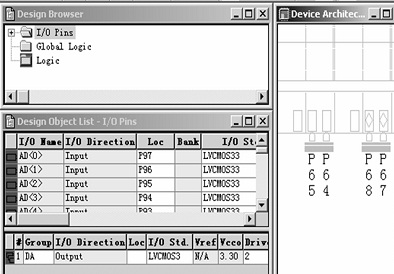

3.3.4.2 ���xݔ��ݔ�����_�s���x��플��ļ����p���D�е�Assign Package Pins��ԓ������(hu��)��ʾϵ�y(t��ng)������һ��(g��).ucf�ļ����x���ǣ�ϵ�y(t��ng)���Ԅ�(d��ng)����(d��ng)Xilinx Pace��

�D 3-13 �������_

�D 3-14 Xilinx Pace

�F(xi��n)�ھͿ�����LOC�ڌ�(xi��)�Ϲ��_�������xI/O�ƽ��ͣ�ݔ�������С�ȣ���Ҫע�����һЩI/O����������̎�ģ����ܺ��y���䡣���x����˳���

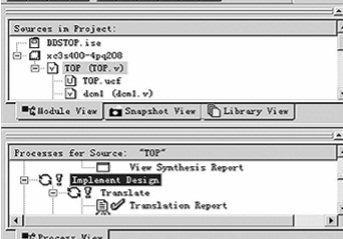

3.3.5 ���ֲ����p��Implement Design����(hu��)���Έ�(zh��)��Translate��Map��Place&Route��

�D 3-15 �O(sh��)Ӌ(j��)��(sh��)�F(xi��n)

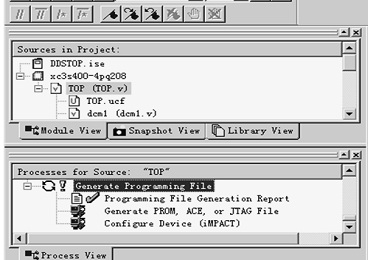

3.3.6 ���d��Ӳ�������x��플��ļ����p���\(y��n)��Generate Programming File���\(y��n)�к���������(y��ng)�ģ�.Bit�����d�ļ���ԓ�ļ������d��оƬ�Ќ�(sh��)�F(xi��n)�O(sh��)Ӌ(j��)��

�D 3-16 �������d�ļ�

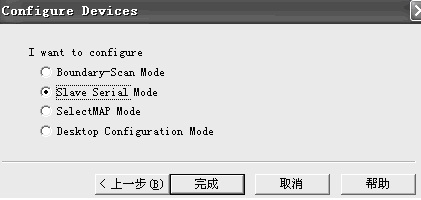

���p���ψDConfigure Device���\(y��n)�к��������d���棬�x���������d��ʽ��Slave Serial Mode�����c(di��n)����ɡ�

�D 3-17 ���d��ʽ

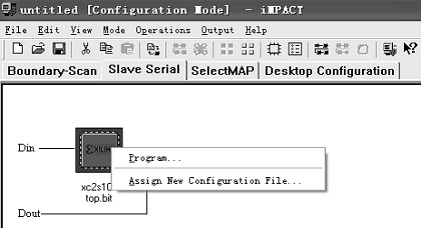

���I�c(di��n)��Ԫ�����c(di��n)��Program���x������(y��ng)��BIT�ļ��_(k��i)ʼ���d��

�D 3-18 ���dλ�ļ�

�ɹ����d��Ϳ�����FPGA�������\(y��n)�к͜y(c��)ԇ�ˡ�

������ ��(sh��)���l��Ӌ(j��)���O(sh��)Ӌ(j��)�c��(sh��)�F(xi��n)4.1 �΄�(w��)Ҫ�����n�}�����΄�(w��)����ɻ���FPGA����VHDL�Z(y��)���O(sh��)Ӌ(j��)һ��(g��)��(sh��)���l��Ӌ(j��)���O(sh��)Ӌ(j��)�����棬���d��(sh��)�F(xi��n)����(sh��)�H�y(c��)��Ч����ͬ�r(sh��)Ҫ��Ϥ������Spartan-II�@�K���ӵĸ��N���ܡ����]�����״ν��|VHDL�����Z(y��)�ԣ�������ǰ�](m��i)���^(gu��)����FPGA�O(sh��)Ӌ(j��)�Ľ�(j��ng)�(y��n)������������n�}��ͬ�r(sh��)��Ҳ����ļ��(du��)VHDL�����Z(y��)�Ե����գ��Լ����࿂�Y(ji��)��ܛ����(l��i)��(sh��)�F(xi��n)Ӳ�������c(di��n)�����Ժ�Ĺ������M(j��n)һ���ČW(xu��)��(x��)�W(xu��)��(x��)��û��A(ch��)���������⣬�����n���r(sh��)�g�W(xu��)��(x��)��(sh��)���l��Ӌ(j��)��Ӳ����(sh��)�F(xi��n)����������MultiSim���棬PROTEL��ԭ��D�Լ�PCB��ȡ���(sh��)���l��Ӌ(j��)�����P(gu��n)���g(sh��)ָ��(bi��o)���£�

1��λ��(sh��)���y(c��)���l��ͨ�^(gu��)LED��(sh��)�a�ܞ���λʮ�M(j��n)�Ɣ�(sh��)�@ʾ��

2���y(c��)ԇ�l�ʷ����飺1Hz��1MHz���U(ku��)չ1MHz��100MHz��

3�����̷֞����n��

��һ�n����С���̙n���l�T(m��n)�r(sh��)�g��1S�r(sh��)������x��(sh��)��999.999KHz��

�ڶ��n���l�T(m��n)�r(sh��)�g��0.1S�r(sh��)������x��(sh��)��9999.99KHz��

�����n���l�T(m��n)�r(sh��)�g��0.01S�r(sh��)������x��(sh��)��99999.9KHz��

�������n,��(sh��)�H�y(c��)�õ��l����1Hz��99999.9KHz���@Ȼ��ȫ���w��1Hz��100MHz�ķ�����

4���@ʾ������ʽ��

a����BCD�߶ι��(y��ng)�O��(sh��)�a���@ʾ�x��(sh��)��ֻ�����x��(sh��)���l(f��)����׃�r(sh��)�������_�ĽY(ji��)����

b������ӛ���@ʾ����������һ�Μy(c��)ԇ�Y(ji��)���r(sh��)���@ʾ�y(c��)ԇ�Y(ji��)�������@ʾֵһֱ�������´Μy(c��)���@ʾ��(sh��)����(l��i)���Ō��ϴ��@ʾ�_ˢ���¡��õڶ��Μy(c��)ԇ�Y(ji��)���������@ʾֵ��

c����(sh��)�F(xi��n)��(du��)��λ�o(w��)���x������[��

5��Ҫ�y(c��)ݔ����̖(h��o)��(y��ng)�Ƿ��ϔ�(sh��)���·Ҫ����}�_�������Ҳ���

4.2 �y(c��)��ԭ������Ӽ��g(sh��)�I(l��ng)���(n��i)���l����һ��(g��)������ą���(sh��)���l���c�����S��늅����Ĝy(c��)���������y(c��)���Y(ji��)������ʮ�����е��P(gu��n)ϵ����ˣ��l�ʵĜy(c��)�����@�ø�����Ҫ.���ң�Ŀǰ����Ӝy(c��)���У��l�ʵĜy(c��)�����_������ߵġ�

4.2.1 �l�ʻ�r(sh��)�g��ԭʼ����(zh��n)�r(sh��)�g��ijһ�r(sh��)���c��һ�r(sh��)��֮�g�ĕr(sh��)�g�L(zh��ng)�ȣ��@��ָ�ĕr(sh��)�����B�m(x��)���ŵĕr(sh��)�g�е�һ��(g��)�r(sh��)�c(di��n)������ʹ����܉�_����ͬһ�r(sh��)�̣�����Ҫʹ�ù�ͬ�ĕr(sh��)�̘�(bi��o)�߁�(l��i)���������@��(g��)�r(sh��)�̘�(bi��o)���ϵĘ�(bi��o)�ȁ�(l��i)���^���J(r��n)�R(sh��)�r(sh��)�̡�ҪӋ(j��)���r(sh��)�g��Ҫ�й̶���׃�ĕr(sh��)�g��λ����������r(sh��)�g�Ļ�����λ�����һ���(n��i)�����(d��ng)��(sh��)���l�ʞ���֪���t���ɴ����(d��ng)��(sh��)�ĵ���(sh��)�õ�����g�����@�����f(shu��)��λ��͘�(bi��o)��(zh��n)�l�ʔ�(sh��)�ǻ������������r(sh��)�̺͕r(sh��)�g�l(f��)չ�Ěvʷ�����з�ӳ����Ķ��x�ڲ���׃�w����Ĝ�(zh��n)�_�Ȳ�����ߡ�

���������^�y(c��)��������õ�̫�(y��ng)���F(xi��n)�����?sh��)�ƽ�����ڞ�ƽ��̫�?y��ng)�ա���̫�(y��ng)�շ֞�24��60��60�ݣ��õ�������������r(sh��)(ӛ�� )�����(zh��n)�_����

)�����(zh��n)�_���� ����(j��)���������D(zhu��n)�ܵ��O�\(y��n)��(d��ng)(�O������Ľ�(j��ng)��׃��)��Ӱ푣�У�����@��(g��)ƫ����õ��ĵ������D(zhu��n)�����ڣ��Q���һ����r(sh��)(ӛ��

����(j��)���������D(zhu��n)�ܵ��O�\(y��n)��(d��ng)(�O������Ľ�(j��ng)��׃��)��Ӱ푣�У�����@��(g��)ƫ����õ��ĵ������D(zhu��n)�����ڣ��Q���һ����r(sh��)(ӛ�� )���ٰѵ������D(zhu��n)�ļ����ԡ�����Ե�׃��(�����_(d��)0.03��)У�����������˵ڶ�����r(sh��)(ӛ��

)���ٰѵ������D(zhu��n)�ļ����ԡ�����Ե�׃��(�����_(d��)0.03��)У�����������˵ڶ�����r(sh��)(ӛ�� )������r(sh��)

)������r(sh��) ��(j��ng)�^(gu��)��ʮ����^�y(c��)���l(f��)�F(xi��n)�䷀(w��n)���Ȟ�

��(j��ng)�^(gu��)��ʮ����^�y(c��)���l(f��)�F(xi��n)�䷀(w��n)���Ȟ� ���@�ӣ���

���@�ӣ��� ���(bi��o)��(zh��n)��Ӌ(j��)�r(sh��)��(zh��n)�_�Ⱥ��y��(y��u)��

���(bi��o)��(zh��n)��Ӌ(j��)�r(sh��)��(zh��n)�_�Ⱥ��y��(y��u)�� ��

�� ���˵õ�����(zh��n)�_�ľ���׃�ĕr(sh��)�g��(bi��o)��(zh��n)���˂���1.900�ؚw���31 556 925 9747��֮һ����v��(sh��)�r(sh��)����(ӛ��ET)�����(zh��n)�_�ȿ��_(d��)

���ҡ�

��ET����^Ӌ(j��)�r(sh��)��(bi��o)��(zh��n)������Ҫ���ܵ������^�y(c��)�����m(x��)���s����(zh��n)�_�����ޡ�

�����(l��i)���M(j��n)���^Ӌ(j��)�r(sh��)��(bi��o)��(zh��n)���@��������ԭ�ӻ���Ӄ�(n��i)���ܼ�(j��)�S�w��ݗ������յ�늴Ų����l���������(zh��n)��(l��i)Ӌ(j��)���r(sh��)�g������ (

( )ԭ�ӻ��B(t��i)�ăɂ�(g��)������(x��)�ܼ�(j��)֮�g�S�w����(du��)��(y��ng)��9 192 631 770��(g��)���ڵij��m(x��)�r(sh��)�g��һ�룬�Դ˞��(bi��o)��(zh��n)�����ĕr(sh��)�g��(bi��o)��(zh��n)�Q��ԭ�ӕr(sh��)(ӛ��AT)�����(zh��n)�_�ȿ��_(d��)

)ԭ�ӻ��B(t��i)�ăɂ�(g��)������(x��)�ܼ�(j��)֮�g�S�w����(du��)��(y��ng)��9 192 631 770��(g��)���ڵij��m(x��)�r(sh��)�g��һ�룬�Դ˞��(bi��o)��(zh��n)�����ĕr(sh��)�g��(bi��o)��(zh��n)�Q��ԭ�ӕr(sh��)(ӛ��AT)�����(zh��n)�_�ȿ��_(d��) ��

�� Ŀǰ����(gu��)�H���ѽ�(j��ng)��(y��ng)�ý�(j��ng)�^(gu��)ԭ�Ә�(bi��o)��(zh��n)�����^(gu��)�ĕr(sh��)�g��(l��i)�l(f��)�͕r(sh��)�g��(bi��o)��(zh��n)����ԭ�ӕr(sh��)��(l��i)��(du��)���ĕr(sh��)(

��ET)�M(j��n)�����������⣬�����l���Ǖr(sh��)�g�ĵ���(sh��)����ˣ����˕r(sh��)�g��(bi��o)��(zh��n)Ҳ�������l�ʘ�(bi��o)��(zh��n)��

���ڔ�(sh��)���·���w�ٰl(f��)չ�͔�(sh��)�ּ����·���ռ������Ӌ(j��)��(sh��)���đ�(y��ng)����ʮ���ռ����������Ӌ(j��)��(sh��)���y(c��)���l�ʾ��о��_�ȸߡ�ʹ�÷��㡢�y(c��)��Ѹ�٣��Լ����ڌ�(sh��)�F(xi��n)�y(c��)���^(gu��)���Ԅ�(d��ng)����һϵ��ͻ����(y��u)�c(di��n)�����Ѱl(f��)չ�ɞ�����l�ʜy(c��)������Ҫ�ֶΡ�

4.2.2 ���Ӌ(j��)��(sh��)���y(c��)�l����Ŀǰ���^�����(sh��)��(sh��)�(y��n)�������Ӌ(j��)��(sh��)�������Мy(c��)���l��(�y(c��)�l)�͜y(c��)������(�y(c��)��)�ȃɷN���ϵĜy(c��)�����ܣ��ʽy(t��ng)�Q��ͨ��Ӌ(j��)��(sh��)��".���N�y(c��)�����ܿ����á������x���_(k��i)�P(gu��n)�����x��

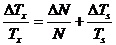

4.2.2.1 ���Ӌ(j��)��(sh��)���Ĝy(c��)�lԭ�����^���l�ʡ���������������̖(h��o)�چ�λ�r(sh��)�g(һ��)��(n��i)׃���ĴΔ�(sh��)������һ���r(sh��)�g��(n��i)Ӌ(j��)���@��(g��)������̖(h��o)׃���ĴΔ�(sh��)��N���t���l�ʿɱ��_(d��)��

(4-1)

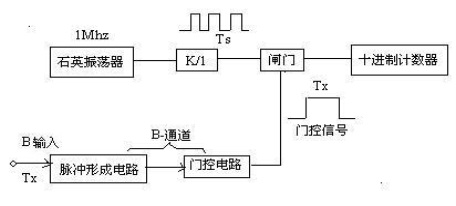

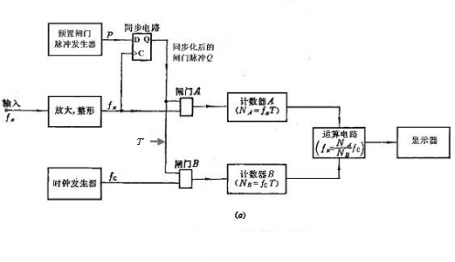

���Ӌ(j��)��(sh��)�����ԇ�(y��n)���չ�ʽ(4-1)�����_(d��)���l�ʵĶ��x�M(j��n)�Мy(c��)�l,��ԭ������D��D 4-1 ʾ��

�D 4-1 �y(c��)�lԭ��D

���ȣ��ѱ��y(c��)��̖(h��o)��(�����Ҳ�����)ͨ�^(gu��)�}�_�γ��·�D(zhu��n)׃���}�_��(��(sh��)�H��׃�ɷ�������)���؏�(f��)�l�ʵ��ڱ��y(c��)�l�� ,Ȼ�����ӵ��l�T(m��n)��һ��(g��)ݔ��ˡ��l�T(m��n)���T(m��n)����̖(h��o)�܁�(l��i)�����_(k��i)���]�r(sh��)�g��ֻ�����l�T(m��n)�_(k��i)ͨ�r(sh��)�gT��(n��i)����Ӌ(j��)��(sh��)���}�_�ݲ���ͨ�^(gu��)�l�T(m��n)�����͵�ʮ�M(j��n)�����Ӌ(j��)��(sh��)���M(j��n)��Ӌ(j��)��(sh��)���T(m��n)����̖(h��o)�����Õr(sh��)�gT�Ƿdz���(zh��n)�_�ģ���������r(sh��)�g����(zh��n)(�r(sh��)��)�����ɕr(sh��)���l(f��)�����ṩ���r(sh��)����̖(h��o)�l(f��)��һ��(g��)�߷�(w��n)����ʯӢ��ʎ����һϵ�Д�(sh��)�ַ��l���M�ɣ�����ݔ���Ę�(bi��o)��(zh��n)�r(sh��)�g�}�_(�r(sh��)��(bi��o))ȥ�����T(m��n)���·�γ��T(m��n)����̖(h��o)�����磬�r(sh��)��(bi��o)��̖(h��o)���؏�(f��)���ڞ�1S���t�ӵ��l�T(m��n)���T(m��n)����̖(h��o)���Õr(sh��)�gT���l�T(m��n)�r(sh��)�g����(zh��n)�_�ص���1s�����l�T(m��n)�_(k��i)ͨ�r(sh��)�g��1s���@�r(sh��)��Ӌ(j��)��10 000��(g��)��(sh��)���t��ʽ(4-1)�����y(c��)�l��

,Ȼ�����ӵ��l�T(m��n)��һ��(g��)ݔ��ˡ��l�T(m��n)���T(m��n)����̖(h��o)�܁�(l��i)�����_(k��i)���]�r(sh��)�g��ֻ�����l�T(m��n)�_(k��i)ͨ�r(sh��)�gT��(n��i)����Ӌ(j��)��(sh��)���}�_�ݲ���ͨ�^(gu��)�l�T(m��n)�����͵�ʮ�M(j��n)�����Ӌ(j��)��(sh��)���M(j��n)��Ӌ(j��)��(sh��)���T(m��n)����̖(h��o)�����Õr(sh��)�gT�Ƿdz���(zh��n)�_�ģ���������r(sh��)�g����(zh��n)(�r(sh��)��)�����ɕr(sh��)���l(f��)�����ṩ���r(sh��)����̖(h��o)�l(f��)��һ��(g��)�߷�(w��n)����ʯӢ��ʎ����һϵ�Д�(sh��)�ַ��l���M�ɣ�����ݔ���Ę�(bi��o)��(zh��n)�r(sh��)�g�}�_(�r(sh��)��(bi��o))ȥ�����T(m��n)���·�γ��T(m��n)����̖(h��o)�����磬�r(sh��)��(bi��o)��̖(h��o)���؏�(f��)���ڞ�1S���t�ӵ��l�T(m��n)���T(m��n)����̖(h��o)���Õr(sh��)�gT���l�T(m��n)�r(sh��)�g����(zh��n)�_�ص���1s�����l�T(m��n)�_(k��i)ͨ�r(sh��)�g��1s���@�r(sh��)��Ӌ(j��)��10 000��(g��)��(sh��)���t��ʽ(4-1)�����y(c��)�l�� =10.000Hz����Ӌ(j��)��(sh��)���φ�λ�@ʾ�顰kHz�����t�@ʾ10.000kHz,��С��(sh��)�c(di��n)��λ�ڵ���λ�����y�O(sh��)�룬���l�T(m��n)�r(sh��)�g�Ğ�T(m��n)=0.1s���tӋ(j��)��(sh��)ֵ��1 000���@��(g��)��(sh��)����10�͵���1s��Ӌ(j��)��(sh��)ֵ����

=10.000Hz����Ӌ(j��)��(sh��)���φ�λ�@ʾ�顰kHz�����t�@ʾ10.000kHz,��С��(sh��)�c(di��n)��λ�ڵ���λ�����y�O(sh��)�룬���l�T(m��n)�r(sh��)�g�Ğ�T(m��n)=0.1s���tӋ(j��)��(sh��)ֵ��1 000���@��(g��)��(sh��)����10�͵���1s��Ӌ(j��)��(sh��)ֵ���� Hz����(sh��)�H�ϣ���(d��ng)��׃�l�T(m��n)�r(sh��)�gT�r(sh��)���@ʾ���ϵ�С��(sh��)�c(di��n)Ҳ�S��������һλ(�Ԅ�(d��ng)��λ)�����@ʾ10.000kHz��

Hz����(sh��)�H�ϣ���(d��ng)��׃�l�T(m��n)�r(sh��)�gT�r(sh��)���@ʾ���ϵ�С��(sh��)�c(di��n)Ҳ�S��������һλ(�Ԅ�(d��ng)��λ)�����@ʾ10.000kHz�� ������ӑՓ��֪�����Ӌ(j��)��(sh��)���Ĝy(c��)�lԭ�팍(sh��)�|(zh��)���Ա��^������A(ch��)������ �͕r(sh��)����̖(h��o)�l����ȣ��ɂ�(g��)�l����ȵĽY(ji��)���Ԕ�(sh��)�ֵ���ʽ�@ʾ����(l��i)��

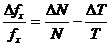

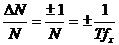

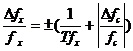

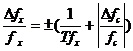

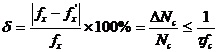

�͕r(sh��)����̖(h��o)�l����ȣ��ɂ�(g��)�l����ȵĽY(ji��)���Ԕ�(sh��)�ֵ���ʽ�@ʾ����(l��i)�� 4.2.3 �`����������҂���(l��i)����Ӌ(j��)��(sh��)���y(c��)�l�Ĝy(c��)���`��Ĺ�ʽ(4-1)��֪�������y(c��)�l�����Ĝy(c��)���`�һ����Q�����l�T(m��n)�r(sh��)�gT��(zh��n)����(zh��n)����һ����Q����Ӌ(j��)��(sh��)��Ӌ(j��)�õĔ�(sh��)��(zh��n)����(zh��n)������(j��)�`��ϳɷ������Ĺ�ʽ(4-1)�ɵ�:

(4-2)

��ʽ(4-2)�е�һ�(xi��ng) �ǔ�(sh��)�ֻ��x�������е��`����ڶ��(xi��ng)

�ǔ�(sh��)�ֻ��x�������е��`����ڶ��(xi��ng) ���l�T(m��n)�r(sh��)�g������(du��)�`��@�(xi��ng)�`��Q����ʯӢ��ʎ�����ṩ�Ę�(bi��o)��(zh��n)�l�ʵĜ�(zh��n)�_�ȡ��F(xi��n)�������¡�

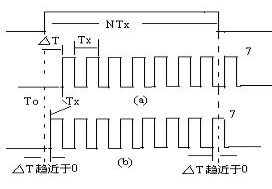

���l�T(m��n)�r(sh��)�g������(du��)�`��@�(xi��ng)�`��Q����ʯӢ��ʎ�����ṩ�Ę�(bi��o)��(zh��n)�l�ʵĜ�(zh��n)�_�ȡ��F(xi��n)�������¡� 4.2.3.1 ��1�`���ڜy(c��)�l�r(sh��)�����T(m��n)���_(k��i)���r(sh��)���cӋ(j��)��(sh��)�}�_֮�g�ĕr(sh��)�g�P(gu��n)ϵ�Dz����P(gu��n)�ģ���������?c��)ڕr(sh��)�g�S�ϵ�����(du��)λ�����S�C(j��)�ġ��@�ӣ�����ͬ�����T(m��n)�_(k��i)���r(sh��)�g��(n��i)��Ӌ(j��)��(sh��)����Ӌ(j��)�õĔ�(sh��)�s��һ����ͬ����(d��ng)���T(m��n)�_(k��i)���r(sh��)�gT�ӽ��������ڱ��y(c��)��̖(h��o)���� ������(sh��)��N���r(sh��)�����(xi��ng)�`�����D 4-2 ��(hu��)���ľ����@�N��r��

������(sh��)��N���r(sh��)�����(xi��ng)�`�����D 4-2 ��(hu��)���ľ����@�N��r�� �D 4-2 ��ؓ(f��)1�`��

�����T(m��n)�_(k��i)���r(sh��)�̞� ������1��(g��)Ӌ(j��)��(sh��)�}�_���F(xi��n)��

������1��(g��)Ӌ(j��)��(sh��)�}�_���F(xi��n)�� ���D 4-2 (a)��ʾ����

���D 4-2 (a)��ʾ���� >

> >0����r(

>0����r( )���@�r(sh��)Ӌ(j��)��(sh��)��Ӌ(j��)��N��(g��)��(sh��)(�D��N=6)���F(xi��n)���ف�(l��i)���D 4-2 (b)��r����

)���@�r(sh��)Ӌ(j��)��(sh��)��Ӌ(j��)��N��(g��)��(sh��)(�D��N=6)���F(xi��n)���ف�(l��i)���D 4-2 (b)��r���� څ����0���@���ЃɷN���ܵ�Ӌ(j��)��(sh��)�Y(ji��)��������1��(g��)Ӌ(j��)��(sh��)�}�_�͵�7��(g��)Ӌ(j��)��(sh��)�}�_����ͨ�^(gu��)���T(m��n)���t��Ӌ(j��)��N+1=7��(g��)��(sh��)��Ҳ�����@�ɂ�(g��)�}�_���](m��i)�����M(j��n)�����T(m��n)���tֻ��Ӌ(j��)��N-1=5��(g��)��(sh��)���ɴ˿�֪������Ӌ(j��)��(sh��)�`���

څ����0���@���ЃɷN���ܵ�Ӌ(j��)��(sh��)�Y(ji��)��������1��(g��)Ӌ(j��)��(sh��)�}�_�͵�7��(g��)Ӌ(j��)��(sh��)�}�_����ͨ�^(gu��)���T(m��n)���t��Ӌ(j��)��N+1=7��(g��)��(sh��)��Ҳ�����@�ɂ�(g��)�}�_���](m��i)�����M(j��n)�����T(m��n)���tֻ��Ӌ(j��)��N-1=5��(g��)��(sh��)���ɴ˿�֪������Ӌ(j��)��(sh��)�`��� ��(g��)��(sh��)�����Կ��]����ʽ(4-1)���Ɍ�(xi��)��

��(g��)��(sh��)�����Կ��]����ʽ(4-1)���Ɍ�(xi��)��

(4-3)

ʽ��T���l�T(m��n)�r(sh��)�g�� �鱻�y(c��)�l�ʡ��Ĺ�ʽ(4-3)��֪������Ӌ(j��)��(sh��)ֵN���٣�������`��ǡ�1��(g��)Ӌ(j��)��(sh��)��λ���ʷQ����1��(g��)���`�����(ji��n)�Q����1�`�������

�鱻�y(c��)�l�ʡ��Ĺ�ʽ(4-3)��֪������Ӌ(j��)��(sh��)ֵN���٣�������`��ǡ�1��(g��)Ӌ(j��)��(sh��)��λ���ʷQ����1��(g��)���`�����(ji��n)�Q����1�`������� һ���r(sh��)�������l�T(m��n)�r(sh��)�gT���ɜpС��1�`�(du��)�y(c��)�l�`���Ӱ푡���(d��ng)T�x����

һ���r(sh��)�������l�T(m��n)�r(sh��)�gT���ɜpС��1�`�(du��)�y(c��)�l�`���Ӱ푡���(d��ng)T�x���� Խ�ͣ��t�ɡ�1�`��a(ch��n)���Ĝy(c��)�l�`��Խ��

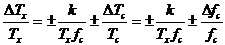

Խ�ͣ��t�ɡ�1�`��a(ch��n)���Ĝy(c��)�l�`��Խ�� 4.2.3.2 ��(bi��o)��(zh��n)�l���`���l�T(m��n)�r(sh��)�gT��(zh��n)����(zh��n)����Ҫ�Q������ʯӢ��ʎ���ṩ�Ę�(bi��o)��(zh��n)�l�ʵĜ�(zh��n)�_�ȣ���ʯӢ��ʎ�����l�ʞ� �����lϵ��(sh��)��k���t

�����lϵ��(sh��)��k���t ��

����

(4-4)

��Ҋ(ji��n)���l�T(m��n)�r(sh��)�g�Ĝ�(zh��n)�_���ڔ�(sh��)ֵ�ϵ��ژ�(bi��o)��(zh��n)�l�ʵĜ�(zh��n)�_�ȣ�ʽ��ؓ(f��)̖(h��o)��ʾ�� ������l�T(m��n)�r(sh��)�g���`���

������l�T(m��n)�r(sh��)�g���`��� ��

�� ͨ������(du��)��(bi��o)��(zh��n)�l�ʜ�(zh��n)�_�� ��Ҫ���Ǹ���(j��)��Ҫ��Ĝy(c��)�l��(zh��n)�_�������(l��i)�ģ����磬��(d��ng)�y(c��)����������СӋ(j��)��(sh��)��λ��1Hz����

��Ҫ���Ǹ���(j��)��Ҫ��Ĝy(c��)�l��(zh��n)�_�������(l��i)�ģ����磬��(d��ng)�y(c��)����������СӋ(j��)��(sh��)��λ��1Hz���� =

= Hz����T=1s�r(sh��)�Ĝy(c��)����(zh��n)�_�Ȟ�

Hz����T=1s�r(sh��)�Ĝy(c��)����(zh��n)�_�Ȟ� (ֻ���]

(ֻ���] �`��)������ʹ��(bi��o)��(zh��n)�l���`���(du��)�y(c��)���Y(ji��)�������a(ch��n)��Ӱ푣�ʯӢ��ʎ����ݔ���l�ʜ�(zh��n)�_��

�`��)������ʹ��(bi��o)��(zh��n)�l���`���(du��)�y(c��)���Y(ji��)�������a(ch��n)��Ӱ푣�ʯӢ��ʎ����ݔ���l�ʜ�(zh��n)�_�� ��(y��ng)��(y��u)��

��(y��ng)��(y��u)�� ������

������ �`������Ĝy(c��)�l�`��Сһ��(g��)����(j��)��

�`������Ĝy(c��)�l�`��Сһ��(g��)����(j��)�� 4.2.3.3 �Y(ji��)Փ�C������,�ɵ����½Y(ji��)Փ��

1��Ӌ(j��)��(sh��)��ֱ�Ӝy(c��)�l���`����Ҫ�Ѓ��(xi��ng)���� �`��͘�(bi��o)��(zh��n)�l���`�һ�㣬���`��ɲ��÷��(xi��ng)�`��^��(du��)ֵ�ϳɣ���

�`��͘�(bi��o)��(zh��n)�l���`�һ�㣬���`��ɲ��÷��(xi��ng)�`��^��(du��)ֵ�ϳɣ���

(4-5)

�ɰѹ�ʽ(4-5)��(hu��)�ɈD 4-3 ��ʾ���������� �cT��

�cT�� �Լ�

�Լ� ���P(gu��n)ϵ������

���P(gu��n)ϵ������ �D 4-3 �`������

�ĈD��֪�� һ���r(sh��)���l�T(m��n)�r(sh��)�gT�x��Խ�L(zh��ng)���y(c��)����(zh��n)�_�Ⱦ�Խ�ߡ�����(d��ng)T�x����

һ���r(sh��)���l�T(m��n)�r(sh��)�gT�x��Խ�L(zh��ng)���y(c��)����(zh��n)�_�Ⱦ�Խ�ߡ�����(d��ng)T�x���� Խ�ߣ��t����

Խ�ߣ��t���� �`�(du��)�y(c��)���Y(ji��)����Ӱ�ԽС���y(c��)����(zh��n)�_�Ⱦ�Խ�ߡ����ǣ��S��

�`�(du��)�y(c��)���Y(ji��)����Ӱ�ԽС���y(c��)����(zh��n)�_�Ⱦ�Խ�ߡ����ǣ��S�� �`��ĜpС����(bi��o)��(zh��n)�l���`��

�`��ĜpС����(bi��o)��(zh��n)�l���`�� ����(du��)�y(c��)���Y(ji��)���a(ch��n)��Ӱ푣�����

����(du��)�y(c��)���Y(ji��)���a(ch��n)��Ӱ푣����� (�D����

(�D���� ����)��O�ޣ����y(c��)����(zh��n)�_�Ȳ����܃�(y��u)��

����)��O�ޣ����y(c��)����(zh��n)�_�Ȳ����܃�(y��u)�� ��

�� 2���y(c��)�����l�r(sh��)������ �`��a(ch��n)���Ĝy(c��)�l�`�����@�ˣ����磬

�`��a(ch��n)���Ĝy(c��)�l�`�����@�ˣ����磬 ��10Hz��T=1s���t��

��10Hz��T=1s���t�� �`������Ĝy(c��)�l�`����_(d��)��10%�����ԣ��y(c��)�����l�r(sh��)���˲���ֱ�Ӝy(c��)�l������

�`������Ĝy(c��)�l�`����_(d��)��10%�����ԣ��y(c��)�����l�r(sh��)���˲���ֱ�Ӝy(c��)�l������ 4.2.4 �y(c��)�����ڵı�Ҫ�Ժͻ���ԭ��4.2.4.1 �y(c��)�����ڵı�Ҫ������ǰ������(d��ng) �^�͕r(sh��)������Ӌ(j��)��(sh��)�y(c��)��ֱ�Ӝy(c��)�l����

�^�͕r(sh��)������Ӌ(j��)��(sh��)�y(c��)��ֱ�Ӝy(c��)�l���� �`��������Ĝy(c��)�l�`���(hu��)�������S�ij̶ȡ����ԣ�������ߜy(c��)�����l�r(sh��)�Ĝ�(zh��n)�_�ȣ����pС

�`��������Ĝy(c��)�l�`���(hu��)�������S�ij̶ȡ����ԣ�������ߜy(c��)�����l�r(sh��)�Ĝ�(zh��n)�_�ȣ����pС �`���Ӱ푣��ɸij��Ȝy(c��)������

�`���Ӱ푣��ɸij��Ȝy(c��)������ ��Ȼ��Ӌ(j��)��

��Ȼ��Ӌ(j��)�� ��?y��n)?img id="aimg_Bf67r" onclick="zoom(this, this.src, 0, 0, 0)" class="zoom" width="19" height="24" src="http://c.51hei.com/a/huq/a/a/c/137/137.097.jpg" border="0" alt="" />Խ�ͣ��tԽ��Ӌ(j��)��(sh��)��Ӌ(j��)�õĔ�(sh��)NҲԽ��

��?y��n)?img id="aimg_Bf67r" onclick="zoom(this, this.src, 0, 0, 0)" class="zoom" width="19" height="24" src="http://c.51hei.com/a/huq/a/a/c/137/137.097.jpg" border="0" alt="" />Խ�ͣ��tԽ��Ӌ(j��)��(sh��)��Ӌ(j��)�õĔ�(sh��)NҲԽ�� �`�(du��)�y(c��)���Y(ji��)����Ӱ���Ȼ�pС��

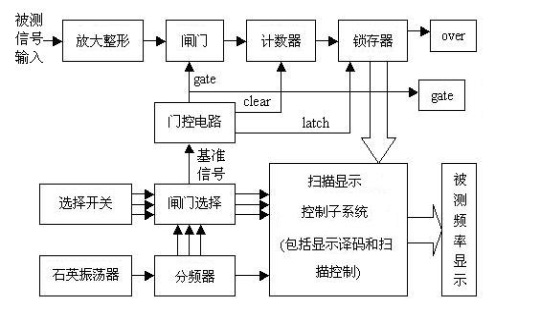

�`�(du��)�y(c��)���Y(ji��)����Ӱ���Ȼ�pС�� 4.2.4.2 �y(c��)�����ڵĻ���ԭ��Ӌ(j��)��(sh��)���y(c��)�����ڵ�ԭ������D��D 4-4 ��ʾ��

�D 4-4 �y(c��)��ԭ��D

���y(c��)��̖(h��o)(����)��Bݔ���ݔ�룬��(j��ng)�}�_�γ��·׃�ɷ������ӵ��T(m��n)���·������ =10ms�t���T(m��n)���_(k��i)10ms���ڴ����g�r(sh��)��(bi��o)�}�_ͨ�^(gu��)���T(m��n)Ӌ(j��)��(sh��)�����x��r(sh��)��(bi��o)��

=10ms�t���T(m��n)���_(k��i)10ms���ڴ����g�r(sh��)��(bi��o)�}�_ͨ�^(gu��)���T(m��n)Ӌ(j��)��(sh��)�����x��r(sh��)��(bi��o)�� �tӋ(j��)��(sh��)��Ӌ(j��)�õ��}�_��(sh��)����

�tӋ(j��)��(sh��)��Ӌ(j��)�õ��}�_��(sh��)���� /

/ =10000��(g��)������ms���λ���t��Ӌ(j��)��(sh��)���@ʾ�Ͽ��x��10.000(ms)��

=10000��(g��)������ms���λ���t��Ӌ(j��)��(sh��)���@ʾ�Ͽ��x��10.000(ms)�� ������ӑՓ��֪��Ӌ(j��)��(sh��)���y(c��)�ܵĻ���ԭ�턂���c�y(c��)�l�෴�����ɱ��y(c��)��̖(h��o)�������T(m��n)�_(k��i)�T(m��n)�����Õr(sh��)��(bi��o)�}�_�M(j��n)��Ӌ(j��)��(sh��)�����Ԍ�(sh��)�|(zh��)��Ҳ��һ�N���^�y(c��)��������

4.2.4.3 �`������c�������Ӌ(j��)��(sh��)���y(c��)�l�r(sh��)���`����ƣ�����(j��)�`����f��ʽ�����Y(ji��)�ψD 4-4�ɵã�

(4-6)

����(j��)�D 4-4 �y(c��)��ԭ��

=

����,��ʽ(4-6)�Ɍ�(xi��)��

(4-7)

�Ĺ�ʽ(4-7)��Ҋ(ji��n)���y(c��)�����ڕr(sh��)���`����_(d��)ʽ�c�y(c��)�l�ı��_(d��)ʽ��ʽ���ƣ������@ ����(�����y(c��)�l������)��

����(�����y(c��)�l������)�� �`�(du��)�y(c��)�ܾ��_�ȵ�Ӱ푾���С��

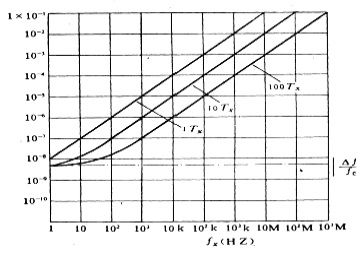

�`�(du��)�y(c��)�ܾ��_�ȵ�Ӱ푾���С�� �D 4-5 ʾ���˜y(c��)�ܕr(sh��)���`���������D�����l����������10 ��100

��100 �ɗl���Dz��ö����ڜy(c��)��(Ԕ��)�r(sh��)���`��������

�ɗl���Dz��ö����ڜy(c��)��(Ԕ��)�r(sh��)���`�������� �D 4-5 �y(c��)�ܕr(sh��)���`������

4.2.4.4 ����(sh��)Ӌ(j��)��(sh��)���y(c��)�����l�r(sh��)�����x�y(c��)�����ڣ�Ȼ����(sh��)�õ����y(c��)�l��ֵ���@�ǜpС�� �`��a(ch��n)���l���`���һ�N��Ч���������ǣ��@�N��������ֱ���x���l��ֵ������Ҫͨ�^(gu��)1/

�`��a(ch��n)���l���`���һ�N��Ч���������ǣ��@�N��������ֱ���x���l��ֵ������Ҫͨ�^(gu��)1/ ��(sh��)�ŵõ��l��ֵ��

��(sh��)�ŵõ��l��ֵ�� ������֪����(sh��)���·Ҳ������ɔ�(sh��)���\(y��n)�㣬���^����(sh��)Ӌ(j��)��(sh��)���������@�NӋ(j��)��(sh��)�������Ȝy(c��)�����ڣ�Ȼ���Ԅ�(d��ng)Ӌ(j��)�㲢�@ʾ���y(c��)�l�ʡ��D 4-6 ʾ����һ�N����(sh��)Ӌ(j��)��(sh��)���ĺ�(ji��n)������D��

�D 4-6 ����(sh��)Ӌ(j��)��(sh��)��

���T(m��n)I��Ӌ(j��)��(sh��)��I�����ڜy(c��)��ģʽ����ݔ���l�� ��(j��ng)�|�l(f��)���ӹ����γ��T(m��n)����̖(h��o)

��(j��ng)�|�l(f��)���ӹ����γ��T(m��n)����̖(h��o) ����

���� �r(sh��)�g��(n��i)���T(m��n)�_(k��i)�����r(sh��)�ͨ�^(gu��)���T(m��n)IӋ(j��)��(sh��)��Ӌ(j��)��

�r(sh��)�g��(n��i)���T(m��n)�_(k��i)�����r(sh��)�ͨ�^(gu��)���T(m��n)IӋ(j��)��(sh��)��Ӌ(j��)�� (

( ���y(c��)��̖(h��o)�����ڣ���

���y(c��)��̖(h��o)�����ڣ��� ��r(sh��)�����)��N���鶨��(bi��o)�����A(y��)��ֵ����������(bi��o)���A(y��)�õ�

��r(sh��)�����)��N���鶨��(bi��o)�����A(y��)��ֵ����������(bi��o)���A(y��)�õ�

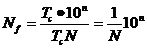

������(bi��o)����(sh��)�|(zh��)������l���ã��r(sh��)�ͨ�^(gu��)�T(m��n)���ɶ���(bi��o)��Ӌ(j��)��(sh��)����(d��ng)Ӌ(j��)��N��(g��)�r(sh��)犺�Ӌ(j��)��(sh��)�������ݔ��һ��(g��)�M(j��n)λ�}�_����ÿӋ(j��)��N��(g��)�r(sh��)�ݔ��һ��(g��)�}�_���ʶ���(bi��o)��ݔ���l�ʞ�

������(bi��o)����(sh��)�|(zh��)������l���ã��r(sh��)�ͨ�^(gu��)�T(m��n)���ɶ���(bi��o)��Ӌ(j��)��(sh��)����(d��ng)Ӌ(j��)��N��(g��)�r(sh��)犺�Ӌ(j��)��(sh��)�������ݔ��һ��(g��)�M(j��n)λ�}�_����ÿӋ(j��)��N��(g��)�r(sh��)�ݔ��һ��(g��)�}�_���ʶ���(bi��o)��ݔ���l�ʞ� �����ڞ�

�����ڞ� ������ͨ�^(gu��)���T(m��n)��Ӌ(j��)��(sh��)�����T(m��n)����l�T(m��n)�r(sh��)�g��

������ͨ�^(gu��)���T(m��n)��Ӌ(j��)��(sh��)�����T(m��n)����l�T(m��n)�r(sh��)�g�� ��Ӌ(j��)��(sh��)��Ӌ(j��)�õĔ�(sh��)��

��Ӌ(j��)��(sh��)��Ӌ(j��)�õĔ�(sh��)��

(4-8)

�y(c��)��ģʽӋ(j��)�õĔ�(sh��)��

(4-9)

�Ĺ�ʽ��4-8����ʽ��4-9����Ҋ(ji��n)��Ӌ(j��)��(sh��)��IIӋ(j��)�õĔ�(sh��) ������N�ĵ���(sh��)���Ķ�����˵���(sh��)���\(y��n)�㣬Ҳ�����f(shu��)���ɏ�Ӌ(j��)��(sh��)��II��ֱ���x���y(c��)�l��

������N�ĵ���(sh��)���Ķ�����˵���(sh��)���\(y��n)�㣬Ҳ�����f(shu��)���ɏ�Ӌ(j��)��(sh��)��II��ֱ���x���y(c��)�l�� �����@ʾ��λ��(sh��)�ɷ��lϵ��(sh��)

�����@ʾ��λ��(sh��)�ɷ��lϵ��(sh��) ����������ʽ(4-9)���빫ʽ(4-8)�ɵ�

����������ʽ(4-9)���빫ʽ(4-8)�ɵ�

(4-10)

�Ĺ�ʽ(4-10)��Ҋ(ji��n),���T(m��n)II��Ӌ(j��)��(sh��)��II��(sh��)�H�Ϲ����ڜy(c��)�lģʽ����ݔ���l�ʾ��� (ע�⣺���ڜy(c��)����ģʽӋ(j��)�õĔ�(sh��)N��������

(ע�⣺���ڜy(c��)����ģʽӋ(j��)�õĔ�(sh��)N�������� �`��ʇ�(y��n)���(l��i)�vݔ���l�ʲ��ǜ�(zh��n)�_�ص���

�`��ʇ�(y��n)���(l��i)�vݔ���l�ʲ��ǜ�(zh��n)�_�ص��� )���ҹ�����ͬ��Ӌ(j��)��(sh��)��ʽ,���ӵ����T(m��n)II��

)���ҹ�����ͬ��Ӌ(j��)��(sh��)��ʽ,���ӵ����T(m��n)II�� ��

�� ͬ��������ͬ��Ӌ(j��)��(sh��)����(hu��)�a(ch��n)��

ͬ��������ͬ��Ӌ(j��)��(sh��)����(hu��)�a(ch��n)�� �`����ԣ�����(sh��)Ӌ(j��)��(sh��)�����`���c�y(c��)��ģʽ�`����ͬ��

�`����ԣ�����(sh��)Ӌ(j��)��(sh��)�����`���c�y(c��)��ģʽ�`����ͬ�� 4.2.5 �Ⱦ��Ȝy(c��)��Ŀǰ�������N���õĔ�(sh��)���l�ʵĜy(c��)������:ֱ�Ӝy(c��)�l��(���º�(ji��n)�QM��)��ֱ�Ӝy(c��)�ܷ�(���º�(ji��n)�QT��)�;C�Ϝy(c��)����(����Y(ji��)�ϵķ��������º�(ji��n)�Q��M/T��)��ǰ�ɷN�y(c��)������ԭ����������Č�(sh��)�(y��n)ԭ�������ѽ�(j��ng)Ԕ��(x��)��ӑՓ�ˣ������������@�ɷN�������`�������֪���侫�ȶ��c���y(c��)��̖(h��o)�����P(gu��n)����������ǷǵȾ��Ȝy(c��)��������M/T����ͨ�^(gu��)�y(c��)�����y(c��)��̖(h��o)��(sh��)��(g��)���ڵĕr(sh��)�g��Ȼ��Q��ó����y(c��)��̖(h��o)���l�ʣ��˷��˜y(c��)�����Ȍ�(du��)���y(c��)��̖(h��o)����ه�ԡ�

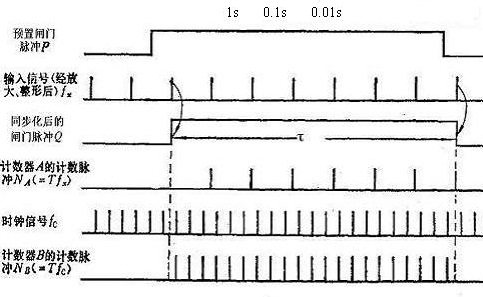

M/T���ĺ���˼����ͨ�^(gu��)�l�T(m��n)��̖(h��o)�c���y(c��)��̖(h��o)ͬ�������l�T(m��n)�r(sh��)�g�ӿ��ƞ鱻�y(c��)��̖(h��o)�����L(zh��ng)�ȵ�����(sh��)�����y(c��)���r(sh��)���ȴ��_(k��i)�A(y��)���l�T(m��n)����(d��ng)�z�y(c��)�����y(c��)��̖(h��o)�}�_�ص��_(d��)�r(sh��)����(bi��o)��(zh��n)��̖(h��o)�r(sh��)��_(k��i)ʼӋ(j��)��(sh��)���A(y��)���l�T(m��n)�P(gu��n)�]�r(sh��)����(bi��o)��(zh��n)��̖(h��o)��������ֹͣӋ(j��)��(sh��)�����ǵșz�y(c��)�����y(c��)��̖(h��o)�}�_�ص��_(d��)�r(sh��)��ֹͣ����ɱ��y(c��)��̖(h��o)����(sh��)��(g��)���ڵĜy(c��)�����y(c��)���Č�(sh��)�H�l�T(m��n)�r(sh��)�g���ܕ�(hu��)�c�A(y��)���l�T(m��n)�r(sh��)�g����ȫ��ͬ��������ֵ����(hu��)���^(gu��)���y(c��)��̖(h��o)��һ��(g��)���ڡ�M/T���y(c��)��ԭ�����D��ʾ��

�D 4-7 ͬ��Ӌ(j��)��(sh��)

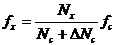

�����(sh��)�H�l�T(m��n)�r(sh��)�g��ӣ����y(c��)��̖(h��o)���ڔ�(sh��)�� ����(bi��o)��(zh��n)��̖(h��o)�l�ʞ�

����(bi��o)��(zh��n)��̖(h��o)�l�ʞ� ��Ӌ(j��)��(sh��)ֵ��

��Ӌ(j��)��(sh��)ֵ�� ���t���y(c��)��̖(h��o)���l��ֵ�飺

���t���y(c��)��̖(h��o)���l��ֵ�飺

(4-11)

���ڌ�(sh��)�H�l�T(m��n)�r(sh��)�g�����ɱ��y(c��)��̖(h��o)ͬ���^(gu��)�ģ�����ڴ����g�y(c��)�õı��y(c��)��̖(h��o)���ڵ�����(sh��)�� �ǜ�(zh��n)�_�ģ�������

�ǜ�(zh��n)�_�ģ������� �`�����(bi��o)��(zh��n)��̖(h��o)��Ӌ(j��)��(sh��)ֵ

�`�����(bi��o)��(zh��n)��̖(h��o)��Ӌ(j��)��(sh��)ֵ �t����

�t���� �`���

�`��� ��(l��i)��t��(bi��o)��(zh��n)��̖(h��o)Ӌ(j��)��(sh��)���挍(sh��)ֵ��

��(l��i)��t��(bi��o)��(zh��n)��̖(h��o)Ӌ(j��)��(sh��)���挍(sh��)ֵ�� +

+ ���ɴ˿�֪���y(c��)��̖(h��o)���l���挍(sh��)ֵ�飺

���ɴ˿�֪���y(c��)��̖(h��o)���l���挍(sh��)ֵ�飺

(4-12)

����Ӌ(j��)��(bi��o)��(zh��n)��̖(h��o)�r(sh��)犵��`��t�y(c��)��������(du��)�`��飺

(4-15)

���Կ�������M/T���У�����(du��)�`���c���y(c��)��̖(h��o)�������l�����ԟo(w��)�P(gu��n)������(du��)����(g��)�y(c��)������ԣ��y(c��)��������ȣ�����Q֮�顰�Ⱦ��Ȝy(c��)��������(bi��o)��(zh��n)��̖(h��o)��Ӌ(j��)��(sh��)ֵ Խ��t�y(c��)������(du��)�`��ԽС��������T(m��n)�ޕr(sh��)�g�Ӻ͘�(bi��o)��(zh��n)��̖(h��o)�l��

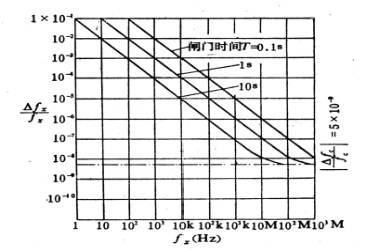

Խ��t�y(c��)������(du��)�`��ԽС��������T(m��n)�ޕr(sh��)�g�Ӻ͘�(bi��o)��(zh��n)��̖(h��o)�l�� ������ߜy(c��)�����ȡ��ھ��Ȳ�׃����r�£���ߘ�(bi��o)��(zh��n)��̖(h��o)�l�ʿ��Կs���T(m��n)�ޕr(sh��)�g����ߜy(c��)���ٶȡ�ԭ��D���£�

������ߜy(c��)�����ȡ��ھ��Ȳ�׃����r�£���ߘ�(bi��o)��(zh��n)��̖(h��o)�l�ʿ��Կs���T(m��n)�ޕr(sh��)�g����ߜy(c��)���ٶȡ�ԭ��D���£� �D 4-8 ͬ�ȶȜy(c��)����ԭ��D

Ӌ(j��)��(sh��)����������(bi��o)��(zh��n)��̖(h��o)���l���A(y��)����̖(h��o)���A(y��)���l�T(m��n)��̖(h��o)�c���y(c��)��̖(h��o)����ͬ��֮��ݔ����(sh��)�H�l�T(m��n)��̖(h��o)����������Ӌ(j��)��(sh��)�����}�_Ӌ(j��)��(sh��)����Ӌ(j��)��(sh��)ʹ����̖(h��o)��ͬ�r(sh��)�ڌ�(sh��)�H�l�T(m��n)��̖(h��o)�P(gu��n)��ĕr(sh��)�g�Ӌ(j��)��(sh��)�������a(ch��n)��һ��(g��)�唵(sh��)�}�_���������Ӌ(j��)��(sh��)����(n��i)��Ӌ(j��)��(sh��)ֵ���Ԃ���һ��Ӌ(j��)��(sh��)��ԓ�����}�_ͬ�r(sh��)߀����һ��Ӌ(j��)��(sh��)�Y(ji��)����Ӌ(j��)��(sh��)ֵ�M(j��n)��Ӌ(j��)�㣬�g�a�@ʾ���i����̖(h��o)����Ȼ����(sh��)�a�ܵ��@ʾ����?y��n)�?sh��)ֵ�IJ�ͣ����(d��ng)���o(w��)���������

�\(y��n)�����tͨ�^(gu��)��ͣ���������\(y��n)�㌍(sh��)�F(xi��n)���y(c��)��̖(h��o)�l��ֵ��Ӌ(j��)�㣬�@ʾ�g�a�����յ����y(c��)��̖(h��o)�l��ֵ��ԓֵ�D(zhu��n)�Q���߶δa��(sh��)��(j��)�@ʾ����ʽ�������Մ�(d��ng)�B(t��i)���跽ʽ���ζ��r(sh��)��ͨ����(g��)�@ʾ�ܣ����@ʾ��(sh��)ֵ�ͳ�,�������۵ĕ���Ч��(y��ng)���Ϳ��Կ�����(w��n)����ݔ��ֵ�ˡ�

4.3 ԭ����D�D 4-9 ԭ����D

4.4 ��ģ�K�Ĺ��ܼ���(sh��)�F(xi��n)4.4.1 ���l�����l���Ĺ������ṩ��(bi��o)��(zh��n)�l�T(m��n)�r(sh��)�g������̖(h��o)�Ծ��_����Ӌ(j��)��(sh��)�����_(k��i)�]�������l�T(m��n)�r(sh��)�gֻ��1S��0.1S��0.01S���n�����ڱ��O(sh��)Ӌ(j��)�����d��Spartan-II�ϣ����ṩ�Ę�(bi��o)��(zh��n)�r(sh��)�g��32MHz����ˣ��҂��뵽��Ӌ(j��)��(sh��)������(du��)һ��(g��)��λ�Ķ��M(j��n)��Ӌ(j��)��(sh��)������(d��ng)ݔ��ɂ�(g��)�}�_�r(sh��)����ݔ���M(j��n)λ�}�_��1��(g��)������/��֮�Ȟ�2��1��������ƣ���(du��)ݔ����2λ��3λ��4λ��5λ�Ķ��M(j��n)��Ӌ(j��)��(sh��)�t��ݔ��/ݔ����1�s4��1�s8��1�s16��1�s32��������ʮ�M(j��n)�����⣬ݔ���m����λ����ݔ��/ݔ���Ȟ�1�s10���@����?y��n)��ڴˣ��?j��)��(sh��)����9�r(sh��)�����a(ch��n)�����M(j��n)λ��

����҂�����һ��(g��)32�M(j��n)�Ƶ�Ӌ(j��)��(sh��)��������(g��)ʮ�M(j��n)��Ӌ(j��)��(sh��)�������B�ӣ���ô���҂�?c��)��������?j��)�ϣ��ɷքe�@��100Hz��10Hz��1Hz�����l�T(m��n)�r(sh��)�g�քe��0.01s��0.1s��1s�Ŀ�����̖(h��o)�����ɵķ��l��ģ�K���D��ʾ��

�D 4-10 ���l��ģ�K

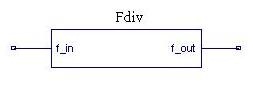

������ʹ�����`�ٺ���(sh��)generic�� Generic ( rate : integer :=10 )�����x��һ��(g��)����׃��rate��ͨ�^(gu��)���@��(g��)����׃��rate��ֵ�����Ԍ�(sh��)�F(xi��n)���l�����l��(sh��)�ĸ�׃���@�������Ԍ�(sh��)�F(xi��n)������{(di��o)�ã�ֻ��Ҫ�������ĵط��Ϳ��Ԍ�(sh��)�F(xi��n)��ͬ�ķ��l��Ҫ��

Դ�������£�

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity fdiv is

Generic ( rate : integer :=10 );

Port ( f_in : In std_logic;

f_out : Out std_logic );

end;

architecture behavioral of fdiv is

signal cnt : integer range 0 to rate := 0;

signal clk : std_logic:='0';

begin

process (f_in)

begin

if f_in'event and f_in = '1' then

if cnt /= rate then

cnt <= cnt + 1;

else

cnt <= 1;

clk<=not clk;

end if;

end if;

end process;

f_out <= clk;

end behavioral;

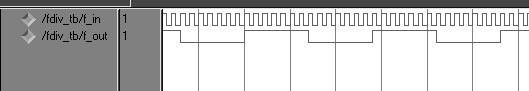

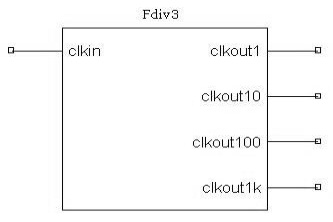

����D������ʾ��

�D 4-11 ���l��ģ�K����D

�\(y��n)��component����(sh��)��(du��)���������{(di��o)�ã����ɺ��p�ɵČ�(sh��)�F(xi��n)�ׂ�(g��)���l�����������ٌ�(xi��)��Ƶij������ɵ�ģ�K��D��ʾ��

�D 4-12 ��ݔ���ķ��l��

�@��(g��)ģ�K����(sh��)�F(xi��n)�˰�32MHz�ĕr(sh��)����̖(h��o)�ֳ����҂���Ҫ���Ă�(g��)��̖(h��o)1Hz��10Hz��100Hz��1KHz����Դ�������£�

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity Fdiv3 is

Port ( clkin : in std_logic;

clkout1 : out std_logic;

clkout10 : out std_logic;

clkout100 : out std_logic;

clkout1k : out std_logic);

end Fdiv3;

architecture structure of Fdiv3 is

component fdiv is

Generic ( rate : integer :=10 );

Port ( f_in : In std_logic;

f_out : Out std_logic );

end component fdiv;

signal carry1,carry2,carry3:std_logic;

begin

U1:fdiv generic map(rate=>16000) port map (f_in=>clkin,f_out=>carry1);

U2:fdiv generic map(rate=>5) port map (f_in=>carry1,f_out=>carry2);

U3:fdiv generic map(rate=>5) port map (f_in=>carry2,f_out=>carry3);

U4:fdiv generic map(rate=>5) port map (f_in=>carry3,f_out=>clkout1);

clkout1K <= carry1;

clkout100 <= carry2;

clkout10<=carry3;

end structure;

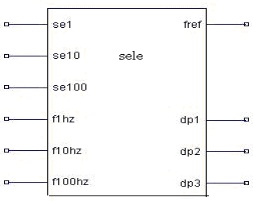

4.4.2 �l�T(m��n)�x����ԓģ�K�Ĺ����nj�(sh��)�F(xi��n)��(du��)ݔ��Ďׂ�(g��)�l�T(m��n)��̖(h��o)���ք�(d��ng)�x��ݔ�����x�е��l�T(m��n)��̖(h��o)�Լ�С��(sh��)�c(di��n)�Ŀ�����̖(h��o)DP1��DP2��DP3�����ɵ�ģ�K���D��ʾ��

�D 4-13 �l�T(m��n)�x����

ԓģ�K������(g��)ݔ��˿ڣ�����se1,se10,se100���x��ʹ�ܶˣ�f1hz,f10hz,f100hz�鱻�x�r(sh��)����̖(h��o)ݔ��ˡ���(d��ng)se1��1�r(sh��)��f1hz��ݔ��r(sh��)����̖(h��o)���x�У����xֵ�oݔ���˿�frefݔ�����˕r(sh��)DP1��Ч��DP2��DP3�o(w��)Ч���c(di��n)��DP1�B�ӵ�С��(sh��)�c(di��n)����(d��ng)se1��0,se10��1�r(sh��)��f10hz�r(sh��)����̖(h��o)���x�У�DP2��Ч��DP1��DP3�o(w��)Ч���c(di��n)����DP2�B�ӵ�С��(sh��)�c(di��n)�����(d��ng)se1��se10���o(w��)Ч�r(sh��)��������0�r(sh��)��se100��1�r(sh��)��f100hz�˿ڵ�ݔ����̖(h��o)���x������ݔ����DP3��Ч��DP1��DP2�o(w��)Ч���c(di��n)����DP3�B�ӵ�С��(sh��)�c(di��n)��

��ģ�K��Դ�������£�

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity sele is

port(se1,se10,se100: in std_logic;

f1hz,f10hz,f100hz: in std_logic;

fref: out std_logic;

dp1,dp2,dp3: out std_logic);

end sele;

architecture Behavioral of sele is

begin

process (se1,se10,se100,f1hz,f10hz,f100hz)

begin

fref <= '0'; dp1 <= '0';dp2 <= '0';dp3 <= '0';

if se1 = '1' then

fref <= f1hz;

dp1<= '1';

elsif se10 = '1' then

fref <= f10hz;

dp2 <= '1';

elsif se100 = '1' then

fref <= f100hz;

dp3 <='1';

end if;

end process;

end Behavioral;

1

������ ��(sh��)���l��Ӌ(j��)���O(sh��)Ӌ(j��)�c��(sh��)�F(xi��n)

����D������ʾ��

�D 4-14 �l�T(m��n)�x��������D

4.4.3 �y(c��)�l�������y(c��)�l�������ǿ�������(g��)�l��Ӌ(j��)��ģ�K�M(j��n)�Еr(sh��)�����Ŀ����b�ã�����(du��)ݔ��Ę�(bi��o)��(zh��n)�r(sh��)���̖(h��o)�M(j��n)��׃�Q���a(ch��n)���҂�����Ҫ������(g��)��̖(h��o)�l�T(m��n)��̖(h��o)GATE���i����̖(h��o)LATCH�Լ�������̖(h��o)CLEAR����ʹ��һ��(g��)���|�l(f��)��̎��1Hz�ĕr(sh��)���̖(h��o)����Q��ݔ���������}��1SӋ(j��)��(sh��)��ʹ�ܶ˵Ŀ�����̖(h��o)���� ݔ�������}��1S���i����ʹ����̖(h��o)��Ӌ(j��)��(sh��)������̖(h��o)Ҳ�ɜy(c��)�l������׃�Q��ݔ������������(g��)�·�������ɵ�Ԫ����̖(h��o)���D��ʾ��

ݔ�������}��1S���i����ʹ����̖(h��o)��Ӌ(j��)��(sh��)������̖(h��o)Ҳ�ɜy(c��)�l������׃�Q��ݔ������������(g��)�·�������ɵ�Ԫ����̖(h��o)���D��ʾ�� �D 4-15 �y(c��)�l������

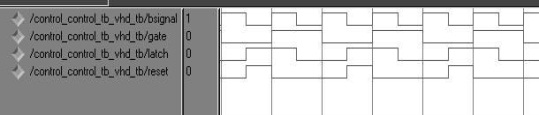

�y(c��)�l������̖(h��o)�l(f��)�����O(sh��)Ӌ(j��)Ҫ���l�ʜy(c��)���Ļ���ԭ����Ӌ(j��)��ÿ��犃�(n��i)���y(c��)��̖(h��o)���}�_��(g��)��(sh��)���@��Ҫ��Control��Ӌ(j��)��(sh��)ʹ����̖(h��o)Gate�ܮa(ch��n)��һ��(g��)������̖(h��o)������(du��)�l��Ӌ(j��)��ÿһӋ(j��)��(sh��)��Counter6��Carry_inʹ�ܶ��M(j��n)��ͬ�����ơ���(d��ng)Gate����ƽ�r(sh��)�����SӋ(j��)��(sh��)������ƽ�r(sh��)ֹͣӋ(j��)��(sh��)������������Ӌ(j��)���}�_��(sh��)����ֹͣӋ(j��)��(sh��)���g��������Ҫһ��(g��)�i����̖(h��o)latch�������،�Ӌ(j��)��(sh��)����ǰ1��犵�Ӌ(j��)��(sh��)ֵ�i���M(j��n)24λ�i����Latch�У������ⲿ��7���g�a���g��������(w��n)���@ʾ���O(sh��)���i�����ĺ�̎�ǣ��@ʾ�Ĕ�(sh��)��(j��)��(w��n)��������(hu��)���������Ե�������̖(h��o)�������W�q���i����̖(h��o)֮�����һ������̖(h��o)Reset��(du��)Ӌ(j��)��(sh��)���M(j��n)�����㣬����1��犵�Ӌ(j��)��(sh��)������(zh��n)�䡣Դ�������£�

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity control is

Port ( Bsignal : in std_logic;

Gate : out std_logic;

Reset : out std_logic;

latch : out std_logic);

end control;

architecture Behavioral of control is

signal G1,G2: std_logic:='0';

begin

process(Bsignal,G1)

begin

if rising_edge(Bsignal) then

G1<=not G1;

end if;

if falling_edge(bsignal) then

G2<=not G1;

end if;

end process;

gate<=G1;

latch<=G2;

reset<=(not bsignal)and(not G1)and (G2);

end Behavioral;

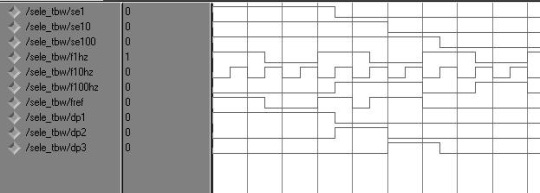

�y(c��)�l������̖(h��o)�l(f��)�����ķ��湤���r(sh��)����D��ʾ��

�D 4-16 �y(c��)�l�������ķ���D

����l�T(m��n)��̖(h��o)Gate���l��ȡ1Hz����ô��̖(h��o)Gate���}��ǡ�Þ�1S����������Ӌ(j��)��(sh��)�l�T(m��n)��̖(h��o)��Ȼ�����(j��)�y(c��)�l�ĕr(sh��)��Ҫ�ɵó���̖(h��o)latch��Reset��߉�������ɈD��Ҋ(ji��n)����Ӌ(j��)��(sh��)��ɺ�Ӌ(j��)��(sh��)ʹ����̖(h��o)Gate��1S�ĸ��ƽ�������䷴��ֵ�a(ch��n)��һ��(g��)�i����̖(h��o)latch�����ڷ������������ӕr(sh��)���i����̖(h��o)������������Ӌ(j��)��(sh��)ʹ����̖(h��o)���l�T(m��n)��̖(h��o)Gate���½���֮����Ӌ(j��)��(sh��)���˲��i��ģ������҂����O(sh��)Ӌ(j��)Ҫ��������̖(h��o)Reset�������صĮa(ch��n)��������һ��(g��)Gate��̖(h��o)������(l��i)�R֮ǰ��Ҳ�����f(shu��)����������_(k��i)ʼӋ(j��)��(sh��)�ģ�����Ӌ(j��)��һ��(hu��)����(sh��)�ٱ��������^�m(x��)Ӌ(j��)��(sh��)���@Ҳ���c�҂����O(sh��)Ӌ(j��)Ҫ������ϵġ����|(zh��)���Ĝy(c��)�l������̖(h��o)�l(f��)�������O(sh��)Ӌ(j��)ʮ����Ҫ���O(sh��)Ӌ(j��)��Ҫ��(du��)���M(j��n)���м�(x��)�Č�(sh��)�r(sh��)���棬��ֹ���ܮa(ch��n)����ë�̡�

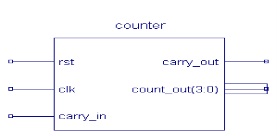

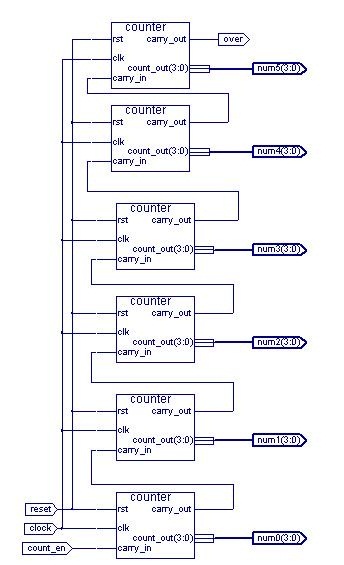

4.4.4 �l��Ӌ(j��)��(sh��)������Ҫ���l��Ӌ(j��)���@ʾ��ʮ�M(j��n)����λ����ʾ�҂�?c��)O(sh��)Ӌ(j��)����ʹ�ܶ˵�ʮ�M(j��n)��Ӌ(j��)��(sh��)���������ɵ�ģ�K��D��ʾ������RST������ˣ�CLK��Ӌ(j��)��(sh��)��̖(h��o)ݔ��ˣ�Carry_in��Ӌ(j��)��(sh��)���ֶˣ�������ƽ�r(sh��)Ӌ(j��)��(sh��)�����ƽ�r(sh��)ֹͣӋ(j��)��(sh��)����Ӌ(j��)��(sh��)��׃��Count_out��Ӌ(j��)��(sh��)�Y(ji��)��ݔ����carry_out���M(j��n)λ��̖(h��o)��

�D�� 4-17 ��(g��)Ӌ(j��)��(sh��)��ģ�K

��Դ����?y��n)�?/font>

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity counter is

port (rst,clk : in std_logic;

carry_in : in std_logic;

carry_out : out std_logic;

count_out : out std_logic_vector(3 downto 0));

end counter;

architecture Behavioral of counter is

signal count: std_logic_vector(3 downto 0):="0000";

begin

process(rst,clk)

begin

if rst='1' then

count <= "0000";

elsif clk'event and clk= '1' then

if carry_in = '1' then

if count < "1001" then

count <= count+1;

else

count <= "0000";

end if;

else

null;

end if;

end if;

end process;

count_out<=count;

carry_out <= '1' when carry_in = '1' and count = "1001" else '0';

end Behavioral;

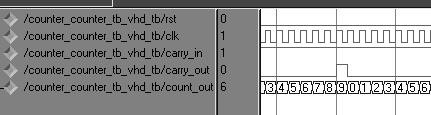

����D���D��ʾ��

�D 4-18 ��(g��)Ӌ(j��)��(sh��)���ķ���D

�ɷ���D���Կ���������ľC�ϳ���(l��i)���@��(g��)Ӌ(j��)��(sh��)���Ĵ_��(sh��)�F(xi��n)�҂��A(y��)����Ҫ��������˺ͱ��ֶˣ�ͨ�^(gu��)��(du��)Ӌ(j��)��(sh��)���ļ�(j��)(li��n)�Ϳ��Ԍ�(sh��)�F(xi��n)ʮ�M(j��n)����λ��(sh��)��Ӌ(j��)��(sh��)��

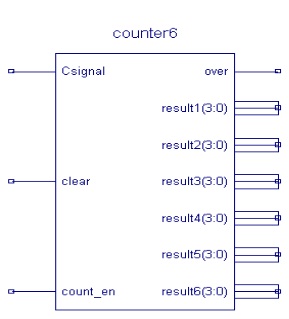

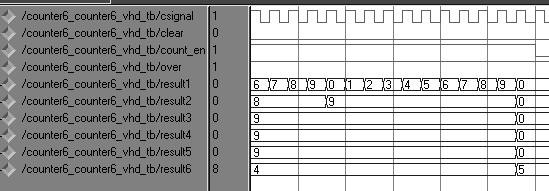

���y(c��)��̖(h��o)������Ӌ(j��)��(sh��)����Csignal�������clear�ͱ��ֶ�count_en�քe�c�y(c��)�l������Reset�˺��l�T(m��n)��̖(h��o)Gate����(du��)�ӡ�Ӌ(j��)��(sh��)��ݔ�����c�i����ݔ��ˌ�(du��)�ӣ����M(j��n)λݔ���˄t���νӵ���һλӋ(j��)��(sh��)���ı��ֶ�cout_en��Ω����λ�����λ���M(j��n)λݔ�����������(bi��o)־��over��(l��i)��ʾ�������@ʾӋ(j��)��(sh��)��Ӌ(j��)��(sh��)�Ƿ����������˾��Q��һ��(j��)�ęnλ���@�ӵļ�(j��)(li��n)�γ���ͬ��Ӌ(j��)��(sh��)����һ�NӋ(j��)��(sh��)�^��ļ�(j��)(li��n)��ʽ�����ɵ�ԭ��ģ�K���£�

�D 4-19 ��(j��)(li��n)���Ӌ(j��)��(sh��)��

Ӌ(j��)��(sh��)��ģ�K��(j��)(li��n)�ij�����l��Ӌ(j��)��(j��)(li��n)������ͬ���@�ﲻ���N�������dȤ�����ѿ��ԅ�����䛡���(j��)(li��n)����λӋ(j��)��(sh��)���ķ���D���£�

�D 4-20 ��λӋ(j��)��(sh��)���ķ���D

4.4.5 �i�������Ӌ(j��)��(sh��)��ݔ��ֱ���c�g�a�����B�ӣ���ô��Ӌ(j��)��(sh��)�^(gu��)����ݔ���˄t�Sݔ���}�_��(sh��)�����Ӷ�������׃����ô�@ʾ��(sh��)�a�܄tҲ��(hu��)�����W�q��׃���˲��ܿ�����(w��n)����ݔ�����O(sh��)�i�����t������׃����������x��Ӌ(j��)��(sh��)�Y(ji��)������control����ģ�K�a(ch��n)����latch��̖(h��o)��(l��i)�ṩ�i���}�_�������ɵĹ���ģ�K��D��ʾ��

�D 4-21 �i����ģ�K

�@ģ�K��(sh��)�F(xi��n)�ˌ�(du��)��λӋ(j��)��(sh��)�Y(ji��)���������̖(h��o)over���i�湦�ܡ�����ܺ�(ji��n)�Σ����i����̖(h��o)��������(l��i)�r(sh��)�͔�(sh��)�������r(sh��)��t���ֲ�׃�����w������䛡�

4.4.6 �����@ʾ�����g�aϵ�y(t��ng)��ģ�Kͨ�^(gu��)��һ��(g��)�l��1KHz����̖(h��o)��(l��i)����һ��(g��)��·�x��������(sh��)�F(xi��n)��(du��)��λ�ѽ�(j��ng)�i���Ӌ(j��)��(sh��)�Y(ji��)���Ē���ݔ��������1KHz����(du��)�����۵ĕ���Ч��(y��ng)�ѽ�(j��ng)�ܸ��ˣ������@ʾ�Y(ji��)������(hu��)�˸��X(ju��)���W�q���@�ӾͿ�����һ��(g��)�g�a����(l��i)��(sh��)�F(xi��n)��(du��)����(g��)4λ���M(j��n)�Ɣ�(sh��)���g�a���g�a�Y(ji��)�����B�ӵ�һ��(g��)��·�x������ݔ��ˣ�ͬ����1KHz����̖(h��o)��(l��i)ͬ�������xͨ��ͬ�r(sh��)��ģ�K߀��(sh��)�F(xi��n)�˟o(w��)���x������[�������ݔ��ȫ��ͨ�^(gu��)���dǰ�Ĺ̶����_�B�ӵ�LED�@ʾ���ϡ���(sh��)�F(xi��n)��K�Y(ji��)���Ĕ�(sh��)���@ʾ��ݔ��˰���������̖(h��o)1KHz����ǰ��a(ch��n)���ڱ�ģ�K��������õ������̖(h��o)Q��over��С��(sh��)�c(di��n)ָʾ��̖(h��o)Dp1,Dp2�Լ��i������ݔ���Y(ji��)����

������ģ�K���£�

�D 4-22 �@ʾ�g�a����ģ�K

��Դ��������:

- library IEEE;

- use IEEE.STD_LOGIC_1164.ALL;

- use IEEE.STD_LOGIC_ARITH.ALL;

- use IEEE.STD_LOGIC_UNSIGNED.ALL;

- entity multi is

- port(f1khz,q_over : in std_logic;

- dp1,dp2 : in std_logic;

- freq_value0,freq_value1 : in std_logic_vector(3 downto 0);

- freq_value2,freq_value3 : in std_logic_vector(3 downto 0);

- freq_value4,freq_value5 : in std_logic_vector(3 downto 0);

- out0,out1,out2,out3,out4,out5: out std_logic_vector(6 downto 0));

- end multi;

- architecture Behavioral of multi is

- signal sel : std_logic_vector(2 downto 0):="000";

- signal hide : std_logic;

- signal data : std_logic_vector(3 downto 0);

- signal led : std_logic_vector(6 downto 0);

- begin

- scan : process (f1khz)

- begin

- if rising_edge(f1khz) then

- if sel = "101" then

- sel <= "000";

- else

- sel <= sel + 1;

- end if;

- end if;

- end process;

- mux:process(sel,freq_value0,freq_value1,freq_value2,freq_value3,freq_value4,freq_value5)

- begin

- case sel is

- when "000" => data <= freq_value0;

- when "001" => data <= freq_value1;

- when "010" => data <= freq_value2;

- when "011" => data <= freq_value3;

- when "100" => data <= freq_value4;

- when others => data <= freq_value5;

- end case;

- end process;

- bcd2led : process (hide,data)

- begin

- led <= "1111111";

- if hide /= '1' then

- case data is

- when "0000" => led <= "0000001";

- when "0001" => led <= "1001111";

- when "0010" => led <= "0010010";

- when "0011" => led <= "0000110";

- when "0100" => led <= "1001100";

- when "0101" => led <= "0100100";

- when "0110" => led <= "0100000";

- when "0111" => led <= "0001111";

- when "1000" => led <= "0000000";

- when "1001" => led <= "0000100";

- when others => null;

- end case;

- end if;

- end process;

- fenpei:process(sel,led)

- begin

- out0<="1111111";

- out1<="1111111";

- out2<="1111111";

- out3<="1111111";

- out4<="1111111";

- out5<="1111111";

- case sel is

- when "000" => out0 <= led;

- when "001" => out1 <= led;

- when "010" => out2 <= led;

- when "011" => out3 <= led;

- when "100" => out4 <= led;

- when "101" => out5 <= led;

- when others => null;

- end case;

- end process;

- hide_zero:process (sel,q_over,dp1,dp2,freq_value5,freq_value4,freq_value3,freq_value2)

- begin

- hide <= '0';

- case sel is

- when "101" =>

- if q_over = '0' and freq_value5 = "0000"

- then hide <= '1';

- end if;

- when "100" =>

- if q_over = '0' and freq_value5 = "0000"

- and freq_value4 = "0000"

- then hide <= '1';

- end if;

- when "011" =>

- if q_over = '0' and freq_value5 = "0000"

- and freq_value4 = "0000"

- and freq_value3 = "0000"

- and dp1 /= '1'

- then hide <= '1';

- end if;

- when "010" =>

- if q_over = '0' and freq_value5 = "0000"

- and freq_value4 = "0000"

- and freq_value3 = "0000"

- and freq_value2 = "0000"

- and dp1 /= '1'

- and dp2 /= '1'

- then hide <= '1';

- end if;

- when others =>

- null;

- end case;

- end process;

- end Behavioral;

����Y(ji��)�����£�

�D 4-23 �@ʾ�g�a����ģ�K�ķ���D

4.5 플�ԭ��D�����������ɵ�ģ�K���҂���Ҫ���B�Ӿ��γ���플�ԭ��D���ٶ��x��ݔ��ݔ�����_���Ϳ��������ľC�Ϻ��O(sh��)Ӌ(j��)��(sh��)�F(xi��n)�ˡ�ԭ��D�^(gu��)�Ʌ�����䛡�

���������ķ��棬��һ��(g��)�Ǿֲ��ķŴڶ���(g��)����Y(ji��)�������w���ڷ���D�Ͽ��Կ�������ľC�ϵĴ_�_(d��)�����҂���Ҫ�������㣬С��(sh��)�c(di��n)�S���l�T(m��n)��׃����׃�������_�@ʾ�Ƿ�������Լ��ɹ���Ӌ(j��)��(sh��)���g�a�@ʾ��

�D 4-24 플�ԭ��D����ľֲ��Ŵ�

�D 4-25 플�ԭ��D����D���w

4.6 �������_�����d��(sh��)�F(xi��n)ȫ������ͨ�^(gu��)���\(y��n)��ISE���O(sh��)Ӌ(j��)��(sh��)�F(xi��n)��Ȼ���ٴ��_(k��i)XILINX PACE��������������_������(sh��)�F(xi��n)�O(sh��)Ӌ(j��)��ݔ��ݔ���˿��c��(sh��)�HоƬ��ݔ��ݔ���˿ڵČ�(du��)��(y��ng)�B�ӡ������߶�LED�ܵĿ�����̖(h��o)���B�ӵ���(sh��)�H�·���߂�(g��)���_����Ҫע�����һЩ�˿��ǹ̶��ģ����ܺ��y���B�ӡ�����r(sh��)����̖(h��o)��ʯӢ��ʎ�����ṩ����̖(h��o)��ֻ����P181ݔ�롣ͬ�r(sh��)߀Ҫ���]��(n��i)���Ŀ�����߉�KCLB�Ĕ�(sh��)���Ƿ��M�����ľC��Ҫ��һ�ж���(zh��n)��;w��Ϳ����\(y��n)��Configure Device���x��Ҫ���d��λ�ļ���.bit������_(k��i)ʼ���d�ˡ�

4.7 �y(c��)ԇ�Y(ji��)���ڳɹ����d���\(y��n)�к��u(p��ng)��ԓ�O(sh��)Ӌ(j��)ϵ�y(t��ng)�Č�(sh��)�H�y(c��)��Ч��������һ�Ό�(du��)�Ȍ�(sh��)�(y��n)���x���l�ʿ��{(di��o)�ĺ���(sh��)�l(f��)����SP1641B��ͬ�r(sh��)��ʾ����TDS210 Tektronix��ͬ���ĸ�ۙ���y(c��)�õĔ�(sh��)��(j��)�ܾ��_��������(sh��)�l(f��)�����Լ�ʾ�������@ʾȫ�Ǻϡ�����l�ʿ��Ԝy(c��)��1Hz�����^(gu��)Ҫ��ݔ����̖(h��o)�ܷ�(w��n)���Ҟ鷽������?y��n)�оƬݔ��˿��Ԏ��������·�����������ޡ��������l�Č�(du��)�Ȝy(c��)���r(sh��)�����ΰl(f��)�����Q����Agilent��˾���a(ch��n)��4410����̖(h��o)Դ���Y(ji��)������ԓ�O(sh��)Ӌ(j��)�Ĵ_�ܜy(c��)����100MHz���y(c��)���Y(ji��)������ԓ�O(sh��)Ӌ(j��)�_(d��)�������������������O(sh��)Ӌ(j��)Ҫ��

������ �Y(ji��)Փ������Ҫ��B������VHDL�Z(y��)����ɻ���FPGA�Ĕ�(sh��)���l��Ӌ(j��)���O(sh��)Ӌ(j��)�c��(sh��)�F(xi��n)��Ԕ��(x��)��B�˜y(c��)��ԭ�����O(sh��)Ӌ(j��)�����Լ���ģ�K���O(sh��)Ӌ(j��)�^(gu��)�̼��䌍(sh��)�F(xi��n)�Ĺ��ܣ�����(du��)�O(sh��)Ӌ(j��)�������Ć�(w��n)�}���˷�����̎��������ISE��ModelSim��(du��)�O(sh��)Ӌ(j��)�M(j��n)���˷��棬�������C�ϣ�����K���d��Spartan-IIϵ��оƬ�У���(sh��)�F(xi��n)�ˌ�(du��)�l�ʵĜy(c��)����

���y(t��ng)��(sh��)���l��Ӌ(j��)�����ڸ��l���ܻ���(zh��n)�r(sh��)��l�ʵ����ƣ���y(c��)�l�����ܵ��ܴ������.���O(sh��)Ӌ(j��)��(y��ng)��EDA���g(sh��)���ܺõĽ�Q���@һ��(w��n)�}.���O(sh��)Ӌ(j��)��ɺ��u(p��ng)��ϵ�y(t��ng)�Č�(sh��)�H�y(c��)��Ч��������һ�Ό�(du��)�Ȍ�(sh��)�(y��n)���y(c��)���Y(ji��)�������y(c��)�����Ȼ������_(d��)�� ���ɝM��һ��y(c��)�����ȵ�Ҫ����(d��ng)���y(c��)��̖(h��o)�l���^�͕r(sh��)���y(c��)ԇ�����^�ͣ��`��׃����ԭ���˔�(sh��)�֜y(c��)����������ؓ(f��)

���ɝM��һ��y(c��)�����ȵ�Ҫ����(d��ng)���y(c��)��̖(h��o)�l���^�͕r(sh��)���y(c��)ԇ�����^�ͣ��`��׃����ԭ���˔�(sh��)�֜y(c��)����������ؓ(f��) �`��͘�(bi��o)��(zh��n)��̖(h��o)������`���⣬߀�l(f��)�F(xi��n)���l��̖(h��o)�������غ��½��ص�׃���^������Ӱ���Ӌ(j��)��(sh��)����Ӌ(j��)��(sh��)ֵ������˜y(c��)�����ȵ��½���

�`��͘�(bi��o)��(zh��n)��̖(h��o)������`���⣬߀�l(f��)�F(xi��n)���l��̖(h��o)�������غ��½��ص�׃���^������Ӱ���Ӌ(j��)��(sh��)����Ӌ(j��)��(sh��)ֵ������˜y(c��)�����ȵ��½��� �@�ǵ�һ������HDL�Z(y��)�ԁ�(l��i)��(sh��)�F(xi��n)����FPGA�Č�(sh��)�H�����(xi��ng)Ŀ�������ڌ�(sh��)�`�^(gu��)���в��ɱ���������˺ܶ���(w��n)�}�Լ��O(sh��)Ӌ(j��)��һЩ����ĵط�����Փ�͌�(sh��)�`�](m��i)���ЙC(j��)��(li��n)ϵ����(l��i)����Փ�](m��i)����(y��ng)�е�ָ��(d��o)���á��籾��(l��i)���Ԍ�(sh��)�F(xi��n)�y(c��)���nλ���Ԅ�(d��ng)�ГQ��ͬ�r(sh��)�ܵ�FPGA���ӱ��������ƣ�С��(sh��)�c(di��n)���ܿ���оƬI/O��ݔ����̖(h��o)����С��(sh��)�c(di��n)��׃��ֻ���������LED��(l��i)�w�F(xi��n)��

���1. Ӌ(j��)��(sh��)����(j��)(li��n)����

- library IEEE;

- use IEEE.STD_LOGIC_1164.ALL;

- use IEEE.STD_LOGIC_ARITH.ALL;

- use IEEE.STD_LOGIC_UNSIGNED.ALL;

- entity counter6 is

- port(Csignal : in std_logic;

- clear : in std_logic;

- count_en : in std_logic;

- over : out std_logic;

- result1 : out std_logic_vector(3 downto 0);

- result2 : out std_logic_vector(3 downto 0);

- result3 : out std_logic_vector(3 downto 0);

- result4 : out std_logic_vector(3 downto 0);

- result5 : out std_logic_vector(3 downto 0);

- result6 : out std_logic_vector(3 downto 0));

- end counter6;

- architecture structure of counter6 is

- component counter is

- port(rst,clk : in std_logic;

- carry_in : in std_logic;

- carry_out : out std_logic;

- count_out : out std_logic_vector(3 downto 0));

- end component counter;

-

- signal carry1,carry2,carry3,carry4,carry5,carry6: std_logic;

- signal over1 :std_logic;

- begin

- U1 : counter Port map ( rst => clear,

- clk => Csignal,

- carry_in => count_en,

- carry_out => carry1,

- count_out => result1 );

- U2 : counter Port map ( rst => clear,

- clk => Csignal,

- carry_in => carry1,

- carry_out => carry2,

- count_out => result2 );

- U3 : counter Port map ( rst => clear,

- clk => Csignal,

- carry_in => carry2,

- carry_out => carry3,

- count_out => result3 );

- U4 : counter Port map ( rst => clear,

- clk => Csignal,

- carry_in => carry3,

- carry_out => carry4,

- count_out => result4 );

- U5 : counter Port map ( rst => clear,

- clk => Csignal,

- carry_in => carry4,

- carry_out => carry5,

- count_out => result5 );

- U6 : counter Port map ( rst => clear,

- clk => Csignal,

- carry_in => carry5,

- carry_out => carry6,

- count_out => result6 );

- process (clear,csignal)

- begin

- if clear = '1' then

- over1<= '0';

- elsif rising_edge(csignal) then

- over1 <= carry6 or over1;

- end if;

- end process;

- over<=over1;

- end structure;

���2. �i����Դ����- library IEEE;

- use IEEE.STD_LOGIC_1164.ALL;

- use IEEE.STD_LOGIC_ARITH.ALL;

- use IEEE.STD_LOGIC_UNSIGNED.ALL;

- entity latch is

- port ( latchin : in std_logic;

- overin : in std_logic;

- numin1 : in std_logic_vector(3 downto 0);

- numin2 : in std_logic_vector(3 downto 0);

- numin3 : in std_logic_vector(3 downto 0);

- numin4 : in std_logic_vector(3 downto 0);

- numin5 : in std_logic_vector(3 downto 0);

- numin6 : in std_logic_vector(3 downto 0);

- overout : out std_logic;

- numout1 : out std_logic_vector(3 downto 0);

- numout2 : out std_logic_vector(3 downto 0);

- numout3 : out std_logic_vector(3 downto 0);

- numout4 : out std_logic_vector(3 downto 0);

- numout5 : out std_logic_vector(3 downto 0);

- numout6 : out std_logic_vector(3 downto 0));

- end latch;

- rchitecture Behavioral of latch is

- begin

- process(latchin)

- begin

- if rising_edge(latchin) then

- overout<=overin;

- numout1<=numin1;

- numout2<=numin2;

- numout3<=numin3;

- numout4<=numin4;

- numout5<=numin5;

- numout6<=numin6;

- end if;

- end process;

- end Behavioral;

���3. 플�ԭ��D

���4. Ӌ(j��)��(sh��)���ļ�(j��)(li��n)�D

������Word��ʽ�ęn51�����d��ַ��

��(sh��)��ʽ�l��Ӌ(j��)���O(sh��)Ӌ(j��)�^(gu��)�̣����а��������õ���VHDl�Z(y��)�Ե�Դ���a���ͷ���D��.rar

(1.77 MB, ���d��(sh��): 41)

��(sh��)��ʽ�l��Ӌ(j��)���O(sh��)Ӌ(j��)�^(gu��)�̣����а��������õ���VHDl�Z(y��)�Ե�Դ���a���ͷ���D��.rar

(1.77 MB, ���d��(sh��): 41)

2019-1-22 16:08 �ς�

�c(di��n)���ļ������d����

���d�e��: �ڎ� -5

����: admin �r(sh��)�g: 2019-1-25 01:44

���Y�ϣ�51�����������!!!

| �gӭ���R (http://www.raoushi.com/bbs/) |

Powered by Discuz! X3.1 |

(4-5)

(4-5)

(4-15)

(4-15)

��(sh��)��ʽ�l��Ӌ(j��)���O(sh��)Ӌ(j��)�^(gu��)�̣����а��������õ���VHDl�Z(y��)�Ե�Դ���a���ͷ���D��.rar

(1.77 MB, ���d��(sh��): 41)

��(sh��)��ʽ�l��Ӌ(j��)���O(sh��)Ӌ(j��)�^(gu��)�̣����а��������õ���VHDl�Z(y��)�Ե�Դ���a���ͷ���D��.rar

(1.77 MB, ���d��(sh��): 41)