可編程時鐘控制器(Programmable Time Controller,PTC),也稱可編程時控器、可編程時控開關,是一種用數字電路技術實現時、分、秒計時的裝置,與機械式時鐘相比具有更高的準確性和直觀性,且無機械裝置,具有更更長的使用壽命,因此得到了廣泛的使用。

可編程時鐘控制器屬自動控制領域的電器件,主要用于在多段時間周期內控制多個電路的開啟或關閉,即具有多周期設置和多觸點輸出。該類產品工業與民用兼顧,智能化程度高且操作簡便。

可編程時鐘控制器從原理上講是一種典型的數字電路,其中包括了組合邏輯電路和時序電路。因此,設計與制做數字鐘就是為了了解數字鐘的原理,從而學會制作數字鐘.而且通過數字鐘的制作進一步的了解在制作中用到的各種中小規模集成電路的作用及實用方法.且由于數字鐘包括組合邏輯電路和時序電路.通過它可以進一步學習與掌握各種組合邏輯電路與時序電路的原理與使用方法.

(一)、設計方案分析

1.分析設計要求,構思總體方案

從題目克制該課題的任務主要有三個方面。其一是設計一個能以數字直接先試試的時鐘電路,該電路要有能夠快速校時的功能;其二是用時鐘信號作為基礎設計一個整點報時的電路;其三是用時鐘信號實現一個工業過程的時間順序控制。可見,課題屬于控制類題目,但并無外部輸入信號,而是由時鐘自動產生動作信號。整個系統可分成三部分,即時鐘電路、整點報時電路、順序控制器電路,而時鐘電路在起控制和主導作用。

2.時鐘電路的構成方案

(1)選用中、小規模集成芯片設計;

3.時間順序控制器

這部分電路都是以時間代碼為輸入信號,經譯碼后產生定時控制信號去推動控制設備工作。譯碼器完成有代碼到控制信號的變換,這里的代碼即時鐘信號代碼,控制信號是驅動控制設備的信號。實現的電路形式是多種多樣的。

(1)利用集成門電路進行設計;

(2)選用合適的現成譯碼器;

(3)用GAL芯片進行編程,實現譯碼;

(4)用存儲器完成譯碼的功能。

怎樣用存儲器完成譯碼功能?可用時鐘電路輸出的時鐘代碼作為存儲器的地址信號,存儲器中存放的數據作為外設工作的控制信號。當時鐘運行到需要外設動作的某一時刻,是存儲器的地址信號及讀信號有效,讀出存儲器中相應的數據信號,每個數據位控制一個外設,若某位數據有效,則相應的外設即可啟動。這種方法簡便,時間容易修改。存儲器可用RAM、EPROM及EEPROM。

外設的形式多種多樣,要求的驅動功率各不相同,因而在譯碼輸出與外設之間必須設置適當的功放電路,以提供外設工作的驅動電流與電壓。應按照所選的具體執行機構選定功放電路。

(二)、確定總體方案

依據上述分析,實現題目要求的電路方案有多種選擇,須要根據各人的條件、要求和其他具體情況權衡利弊,確定其中的一種。這里選擇兩種不同方案作具體電路設計。

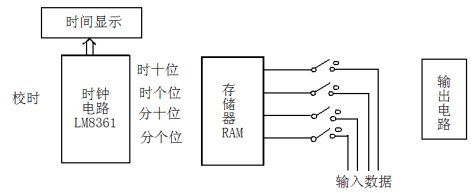

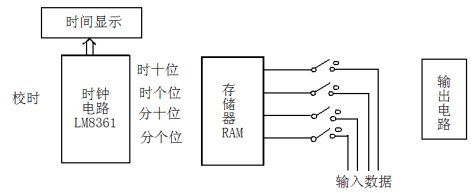

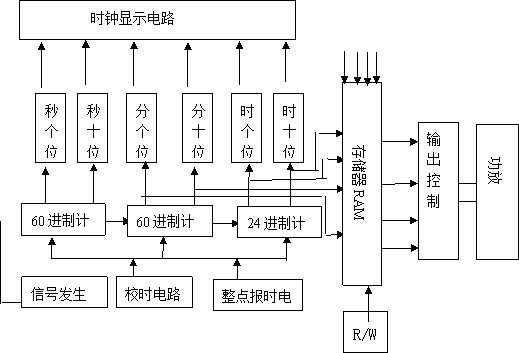

設計方案一采用的是大規模時鐘集成芯片LM8361作時鐘電路,用存儲器RAM6264作譯碼器,設計工藝流程控制電路。其系統框圖如下圖所示:

圖3-2-1 大規模順序控制器框圖

2.設計方案二

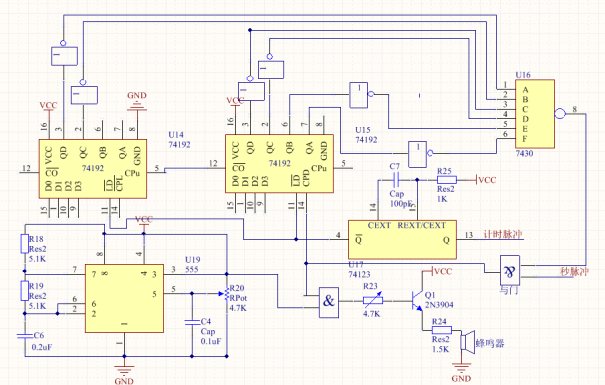

設計方案二采用的是用中小規模門電路構成的時鐘電路,采用的是555定時器作為時基電路,發出1HZ的脈沖作為秒的輸入脈沖,用74LS192設計24、60進制的計數器,用72LS248作為譯碼器,使用7段數碼管來顯示時間,利用門電路構建快速校時電路,用RAM62256存儲器作譯碼器設計可編程時間順序控制器。系統框圖如圖3-2-2所示。

圖3-2-2 鐘控順序控制器框圖

3.最終方案的選擇

作為課程設計的方案,應該具有設計成本較低,可操作性強,與課程學習有較為緊密的聯系等優點。由于大規模集成芯片價格較為昂貴,且可操作性較差,在實際學習中用到的機會比較少,所以方案一不適合作為本次課程設計的方案,而方案二采用的是小規模集成芯片和門電路作為電路設計的基礎,具有較強的可操作性,且價格較為低廉,而所使用的芯片,門電路都是在學習中使用較為頻繁的部分,所以本次課程設計采用的是方案二,利用中西規模門電路構成時鐘電路,用RAM62256存儲器作為譯碼器設計可編程順序控制器。

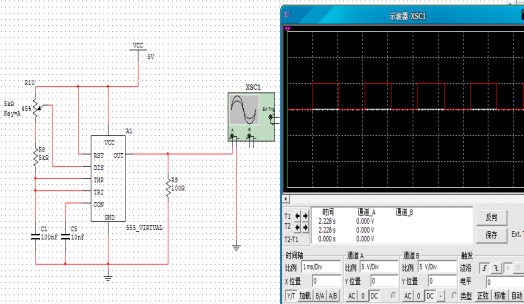

圖3-2-9 555定時器組成的時基電路

555定時器成本低,性能可靠,只需要外接幾個電阻、電容,就可以實現多諧振蕩器、單穩態觸發器及施密特觸發器等脈沖產生與變換電路。它也常作為定時器廣泛應用于儀器儀表、家用電器、電子測量及自動控制等方面。555 定時器的內部電路框圖如圖 2.9.1。它內部包括兩個電壓比較器,三個等值串聯電阻,一個 RS 觸發器,一個放電管 T 及功率輸出級。它提供兩個基準電壓VCC /3 和 2VCC /3

555 定時器的功能主要由兩個比較器決定。兩個比較器的輸出電壓控制 RS 觸發器和放電管的狀態。在電源與地之間加上電壓,當 5 腳懸空時,則電壓比較器 C1 的同相輸入端的電壓為 2VCC /3,C2 的反相輸入端的電壓為VCC /3。若觸發輸入端 TR 的電壓小于VCC /3,則比較器 C2 的輸出為 0,可使 RS 觸發器置 1,使輸出端 OUT=1。如果閾值輸入端 TH 的電壓大于 2VCC/3,同時 TR 端的電壓大于VCC /3,則C1 的輸出為 0,C2 的輸出為 1,可將 RS 觸發器置 0,使輸出為 0 電平。

它的各個引腳功能如下:

1腳:外接電源負端VSS或接地,一般情況下接地。

8腳:外接電源VCC,雙極型時基電路VCC的范圍是4.5 ~ 16V,CMOS型時基電路VCC的范圍為3 ~ 18V。一般用5V。

3腳:輸出端Vo; 2腳:低觸發端

6腳:TH高觸發端

4腳:是直接清零端。當此端接低電平,則時基電路不工作,此時不論TR、TH處于何電平,時基電路輸出為“0”,該端不用時應接高電平。

5腳:VC為控制電壓端。若此端外接電壓,則可改變內部兩個比較器的基準電壓,當該端不用時,應將該端串入一只0.01μF電容接地,以防引入干擾。

7腳:放電端。該端與放電管集電極相連,用做定時器時電容的放電。

利用555定時器產生1HZ的脈沖作為秒信號如下圖:

(1)74ls192介紹

74192是雙時鐘的十進制可逆計數器。(BCD二進制),下面我們介紹74192引腳圖,74192功能表等。

CPU為加計數器時鐘入端,CPU為減計數器入端;

LD為預置輸入控制端,異步預置;

CR為復位輸入端,高電平有效,異步清除;

CO為進位輸出:1001狀態后負脈沖輸出;

BO為借位輸出:0000狀態后負脈沖輸出;

(2)功能表:

(3)引腳圖:

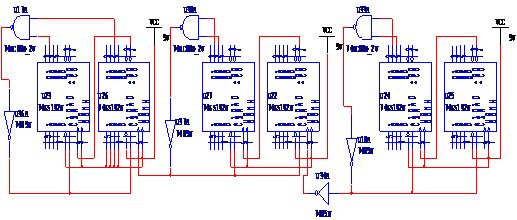

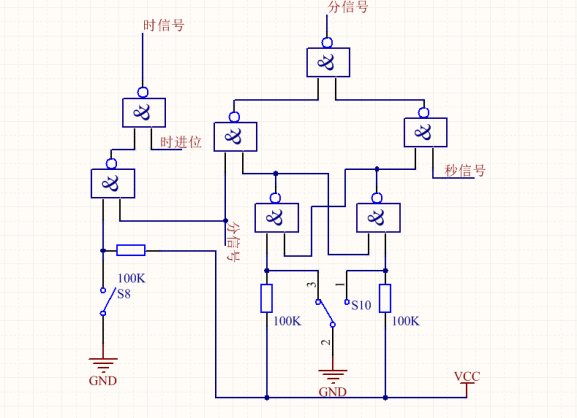

(4)十、分、秒電路總體結構圖

(5)60進制計數器單元仿真電路圖

電路分析:

由555定時器產生1HZ脈沖作為輸入,將74ls192接成60進制計數器,經過74ls248譯碼后由七段數碼管顯示出時鐘信號,構成了60進制的時鐘電路。

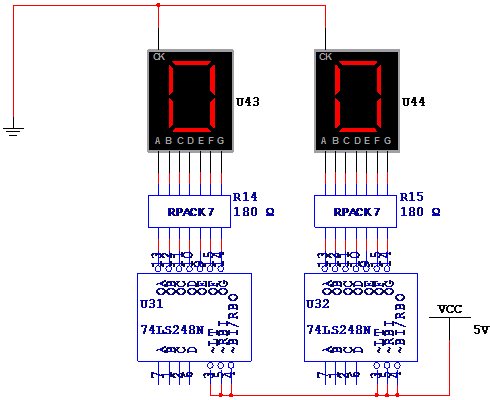

2位譯碼顯示電路單元仿真電路圖如下圖:

圖3-2-12-0

電路分析:

如上圖所示,由74LS248芯片以及共陰極七段數碼管構成譯碼顯示電路,由74248的ABCD接收計數器的數值經轉換后得到七位的七段數碼管顯示值,由共陰極七段數碼管顯示最終數值。

圖3-2-14 整點報時電路

本電路設計簡潔、實用,大部分模塊單元選用集成運放電路。在時基電路中采用集成NE555, 在時間計數器電路中采用集成芯片CT74192,在譯碼、驅動及顯示電路中采用集成芯片74LS248。如此設計使得電路外圍結構簡單,體積小巧精致,且較好的結合了各運放的優良性能,使電路能滿足各項指標。現介紹各芯片列表如下:

五、設計方案總結

實驗過程中遇到的問題及解決方法:

① 元器件的選擇不存在問題。

② 七段顯示器與驅動器連接的測量時, 有時有些數字顯示斷開、 不完整。 原因可能是數碼管引腳接觸不良,或者是通關數碼管的電流過大 需 要接入排阻。 在接電路時譯碼管的電源和接地的沒接, 直接導致譯碼 管無法工作,數碼管無數字顯示。

③ 時間計數電路的連接與測試 仔細的連接電路是非常重要的,不要忘了電源和接地的引腳連接線。 測試時秒 計數顯示無法進位、跳動還較快,無法進位是因為在 74LS08D 集成管的輸入輸出弄錯引腳, 跳動較快是因為把 4060BP 和 74LS74D 的接線引腳接在了 4060BP 的 2 引腳。 經檢查發現接線錯誤 調整后,時間秒顯示正常。

④ 校正電路 校正時有時單獨校正分,時會跟著調動,原因是分與時的進位接線沒 斷開。

六、心得體會

通過這次實訓,讓我們更加了解了各種集成塊的應用,也對其中一 些集成塊的用途有了一定的了解。實訓對于我們的動手設計能力也是一 種提高,細心,認真在其尤其重要。對于一些容易遺漏的引腳,如電源, 接地引腳特別要注意。 該電路的設計讓我對數字鐘的設計有了一定的了解。我知道了如何 設計出 1HZ 的信號,也對時分秒的設計有了一定的了解。并且在實際電 路一般步驟為由數字鐘系統組成框圖按照信號的流向分級安裝,逐級級 聯,這里的每一級是指組成數字鐘的各功能電路。級聯時如果出現時序 配合不同步,或尖峰脈沖干擾,引起邏輯混亂,可以增加多級邏輯門來 延時。經過聯調并糾正設計方案中的錯誤和不足之處后,再測試電路的邏輯功能是否滿足設計要求。 最后畫出滿足設計要求的總體邏輯電路圖。

完整的Word格式文檔51黑下載地址(內含清晰大圖):

可編程時鐘控制器的設計 - (2).doc

(430.5 KB, 下載次數: 12)

可編程時鐘控制器的設計 - (2).doc

(430.5 KB, 下載次數: 12)

| 歡迎光臨 (http://www.raoushi.com/bbs/) | Powered by Discuz! X3.1 |