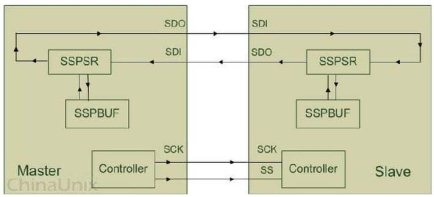

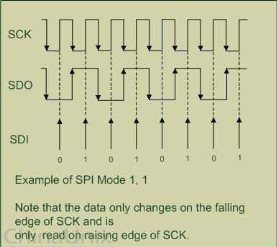

SPI ��һ���h(hu��n)�ο����Y(ji��)��(g��u)�������ķ�ʽ�������@�Nģʽͨ����һ�����O(sh��)���һ������� ���O(sh��)�䣬��Ҫ���� 4 ����(�����ݔ�r��3 ����Ҳ���ԣ�����ss��cs����sck��sdi��sdo ��(g��u)�ɣ� ��r���䌍(sh��)�ܺ��Σ���Ҫ���� sck �Ŀ����£��ɂ��p����λ�Ĵ����M(j��n)�Д�(sh��)��(j��)���Q�����S MCU ��ȫ�p����ͬ�����з�ʽ��ֻҎ(gu��)����ÿһ����(sh��)��(j��)���ݔ����δ�����Y(ji��)��(g��u)�ĽM������B��

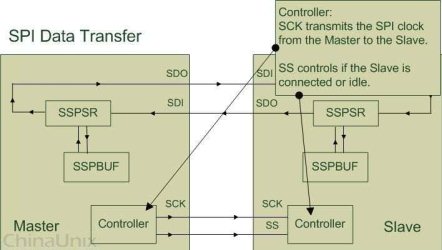

�ɂ� SPI �O(sh��)��֮�gͨ�ű�������O(sh��)������ƴ��O(sh��)�䡣һ�����O(sh��)�����ͨ�^�ṩ Clock �� �������O(sh��)���M(j��n)��Ƭ�x(SlaveSelect/ss)�����ƶ������O(sh��)�䣬SPI �f(xi��)�h߀Ҏ(gu��)�����O(sh��)��� Clock �� Master �O(sh��)��ͨ�^ SCK ���_�ṩ�o���O(sh��)�䣬���O(sh��)�䱾�����ܮa(ch��n)������� Clock���]�� Clock �t���O(sh��)�䲻������������

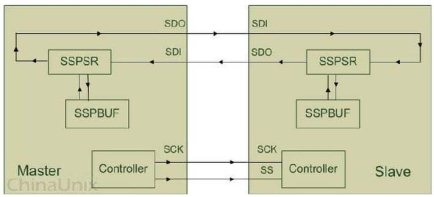

Master �O(sh��)�������(j��)��Ҫ���Q�Ĕ�(sh��)��(j��)���a(ch��n)������(y��ng)�ĕr��}�_(ClockPulse)���r��}�_�M�� �˕r���̖(Clock Signal)���r���̖ͨ�^�r犘O��(CPOL)�͕r���λ(CPHA)�������ɂ� SPI �O(sh��)���g�Εr��(sh��)��(j��)���Q�Լ��Εr�����յ��Ĕ�(sh��)��(j��)�M(j��n)�вɘӣ������C��(sh��)��(j��)�ڃɂ��O(sh��)��֮�g��ͬ�� ��ݔ?sh��)ġ?/font>

SPI �O(sh��)���g�Ĕ�(sh��)��(j��)��ݔ֮�����ֱ��Q�锵(sh��)��(j��)���Q������?y��n)?SPI �f(xi��)�hҎ(gu��)��һ�� SPI �O(sh��)�䲻 ���ڔ�(sh��)��(j��)ͨ���^���ЃH�Hֻ�䮔(d��ng)һ��"�l(f��)����(Transmitter)"����"������(Receiver)"����ÿ�� Clock ���ڃ�(n��i)��SPI �O(sh��)�䶼���l(f��)�Ͳ�����һ�� bit ��С�Ĕ�(sh��)��(j��)���ஔ(d��ng)��ԓ�O(sh��)����һ�� bit ��С �Ĕ�(sh��)��(j��)�����Q�ˡ�

һ�����O(sh��)��Ҫ���܉���յ� Master �l(f��)�^���Ŀ�����̖������ڴ�֮ǰ�܉� Master �O(sh��) ���M(j��n)���L��(Access)�����ԣ�Master �O(sh��)��������ͨ�^ SS/CSpin �����O(sh��)���M(j��n)��Ƭ�x������Ҫ �L���ď��O(sh��)���x�ϡ�

���յ��Ĕ�(sh��)��(j��)�]�б��xȡ����ô�@Щ�ѽ�(j��ng)������ɵĔ�(sh��)��(j��)���п��ܕ����G������(d��o)�� SPI ���� ģ�K��KʧЧ����ˣ��ڳ�����һ�㶼���� SPI ��ݔ�ꔵ(sh��)��(j��)��ȥ�xȡ SPI �O(sh��)����Ĕ�(sh��)��(j��)�� ��ʹ�@Щ��(sh��)��(j��)(Dummy Data)���҂��ij������ǟo�õġ�

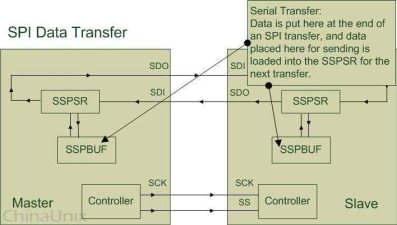

SSPBUF��Synchronous Serial Port Buffer������ָ SPI �O(sh��)������ă�(n��i)�����_�^(q��)��һ������ �������� FIFO ����ʽ������?zh��n)�ݔ�^���е��R�r��(sh��)��(j��)��

Controller����ָ SPI �O(sh��)������Ŀ��ƼĴ���������ͨ�^�����������O(sh��)�� SPI �����Ă�ݔ ģʽ��

ͨ����r�£��҂�ֻ��Ҫ���ψD���������Ă����_(pin)�M(j��n)�о��̼��ɿ������� SPI �O(sh��)�� ֮�g�Ĕ�(sh��)��(j��)ͨ�ţ�SCK��Serial Clock����Ҫ�������� Master �O(sh��)�������O(sh��)���ݔ�r���̖�� ���Ɣ�(sh��)��(j��)���Q�ĕr�C(j��)�Լ����ʣ�

SS/CS��Slave Select/Chip Select������ Master �O(sh��)��Ƭ�x���O(sh��)�䣬ʹ���x�еď��O(sh��)���܉� �� Master �O(sh��)�����L����

SDO/MOSI��Serial Data Output/Master Out Slave In���� Master ����Ҳ���Q�� Tx-Channel�� ���锵(sh��)��(j��)�ij��ڣ���Ҫ���� SPI �O(sh��)��l(f��)�͔�(sh��)��(j��)��

SDI/MISO��Serial Data Input/Master In Slave Out���� Master ����Ҳ���Q�� Rx-Channel�� ���锵(sh��)��(j��)����ڣ���Ҫ���� SPI �O(sh��)����Ք�(sh��)��(j��)��

CPOL���r犘O�ԣ���ʾ SPI �ڿ��e�r���r���̖�Ǹ��ƽ߀�ǵ��ƽ���� CPOL ���O(sh��) �� 1����ôԓ�O(sh��)���ڿ��e�r SCK ���_�µĕr���̖����ƽ����(d��ng)CPOL ���O(sh��)�� 0 �r�t���� �෴��

CPHA���r���λ����ʾ SPI �O(sh��)������ SCK ���_�ϵĕr���̖׃?y��u)������ؕr�|�l(f��)��(sh��)��(j��) �ɘӣ�߀���ڕr���̖׃?y��u)��½��ؕr�|�l(f��)��(sh��)��(j��)�ɘӡ��� CPHA ���O(sh��)�Þ� 1���t SPI �O(sh��)���ڕr ���̖׃?y��u)��½��ؕr�|�l(f��)��(sh��)��(j��)�ɘӣ��������ؕr�l(f��)�͔�(sh��)��(j��)����(d��ng) CPHA ���O(sh��)�� 0 �rҲ������ ����

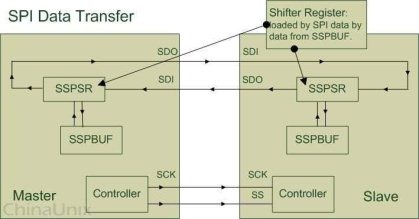

SSPSR �� SPI �O(sh��)���(n��i)������λ�Ĵ���(ShiftRegister)��������Ҫ�����Ǹ���(j��) SPI �r���̖ ��B(t��i) �� �� SSPBUF �� ������� �Ƴ���(sh��)��(j��) �� ÿ���Ƅӵ� ��(sh��)��(j��)��С�� Bus-Width �Լ� Channel-Width ���Q����

Bus-Width ��������ָ����ַ������ Master �O(sh��)��֮�g��(sh��)��(j��)��ݔ?sh��)Ć�λ�?���磬�҂���Ҫ�� Master �O(sh��)������� SSPBUF ���� 16Byte ��С�Ĕ�(sh��)��(j��)�����ȣ��oMaster

�O(sh��)������üĴ����O(sh��)�� Bus-Width �� Byte��Ȼ���� Master �O(sh��)��� Tx-Data ��λ�Ĵ����ڵ� ַ��������ڌ��딵(sh��)��(j��)��ÿ�Ό��� 1Byte ��С�Ĕ�(sh��)��(j��)(ʹ�� writeb ����(sh��))������ 1Byte ��(sh��)��(j��)֮ ��Master �O(sh��)������� Tx-Data ��λ�Ĵ������ԄӰяĵ�ַ���������� 1Byte ��(sh��)��(j��)���� SSPBUF ���������һ����Ҫ�؏�(f��)��(zh��)�� 16�Ρ�

Channel-Width ��������ָ�� Master �O(sh��)���c���O(sh��)��֮�g��(sh��)��(j��)��ݔ?sh��)Ć�λ���c Bus-Width ���ƣ�Master �O(sh��)���(n��i)������λ�Ĵ���������(j��) Channel-Width �Ԅӵذє�(sh��)��(j��)�� Master-SSPBUF ��ͨ�^ Master-SDO ���_���\(y��n)�����O(sh��)����� Slave-SDI ���_��Slave��SSPSR �ٰ�ÿ�ν��յ� ��(sh��)��(j��)���� Slave-SSPBUF �

ͨ����r�£�Bus-Width ���Ǖ����ڻ���� Channel-Width���@���ܱ��C�������F(xi��n)�� Master �c Slave ֮�g��(sh��)��(j��)���Q���l�ʱȵ�ַ�����c Master ֮�g�Ĕ�(sh��)��(j��)���Q�l��Ҫ�죬��(d��o)�� SSPBUF �����ŵĔ�(sh��)��(j��)��oЧ��(sh��)��(j��)�@�ӵ���r��

�҂�֪������ÿ���r����ڃ�(n��i)��Master �c Slave ֮�g���Q�Ĕ�(sh��)��(j��)�䌍(sh��)���� SPI ��(n��i)����λ �Ĵ����� SSPBUF ���濽ؐ�ġ��҂�����ͨ�^�� SSPBUF ����(y��ng)�ļĴ���(Tx-Data/Rx-Data register)���x����(sh��)��(j��)���g�ӵزٿ� SPI �O(sh��)���(n��i)���� SSPBUF�����磬�ڰl(f��)�͔�(sh��)��(j��)֮ǰ���҂� ��(y��ng)ԓ���� Master �� Tx-Data �Ĵ������댢Ҫ�l(f��)�ͳ�ȥ�Ĕ�(sh��)��(j��)���@Щ��(sh��)��(j��)���� Master-SSPSR ��λ�Ĵ�������(j��) Bus-Width �Ԅ����� Master-SSPBUF �Ȼ���@Щ��(sh��)��(j��)�֕��� Master-SSPSR ����(j��) Channel-Width�� Master-SSPBUF ���Ƴ���ͨ�^ Master-SDO ���_���o Slave-SDI ���_�� Slave-SSPSR �t�я� Slave-SDI ���յ��Ĕ�(sh��)��(j��)���� Slave-SSPBUF �� �� �c��ͬ�r ��Slave-SSPBUF ����Ĕ�(sh��)��(j��)����(j��)ÿ�ν��Ք�(sh��)��(j��)�Ĵ�С(Channel-Width)��ͨ�^ Slave-SDO �l(f��)��

Master-SDI��Master-SSPSR �ٰя� Master-SDI ���յĔ�(sh��)��(j��)���� Master-SSPBUF���چδΔ�(sh��) ��(j��)��ݔ���֮���Ñ��������ͨ�^�� Master �O(sh��)��� Rx-Data �Ĵ����xȡ Master �O(sh��)�䔵(sh��)��(j��) ���Q�õ��Ĕ�(sh��)��(j��)��

Master �O(sh��)�� ����� Controller ��Ҫͨ�^�r���̖(ClockSignal)�Լ�Ƭ�x��̖(SlaveSelect Signal)�����Ə�

Master �O(sh��)�� ����� Controller ��Ҫͨ�^�r���̖(ClockSignal)�Լ�Ƭ�x��̖(SlaveSelect Signal)�����Ə�

�O(sh��)�䡣���O(sh��)���һֱ�ȴ���ֱ�����յ� Master �O(sh��)��l(f��)�^����Ƭ�x��̖��Ȼ�����(j��)�r���̖ ��������

Master �O(sh��)���Ƭ�x��������ɳ�������(sh��)�F(xi��n)�����磺�ɳ���� SS/CS ���_�ĕr���̖�� ���ƽ����� SPI �O(sh��)�䔵(sh��)��(j��)ͨ�ŵ�ǰ�ڹ�������(d��ng)������ SPI �O(sh��)��Y(ji��)����(sh��)��(j��)ͨ�ŕr���ٰ� SS/CS ���_�ϵĕr���̖�����ƽ

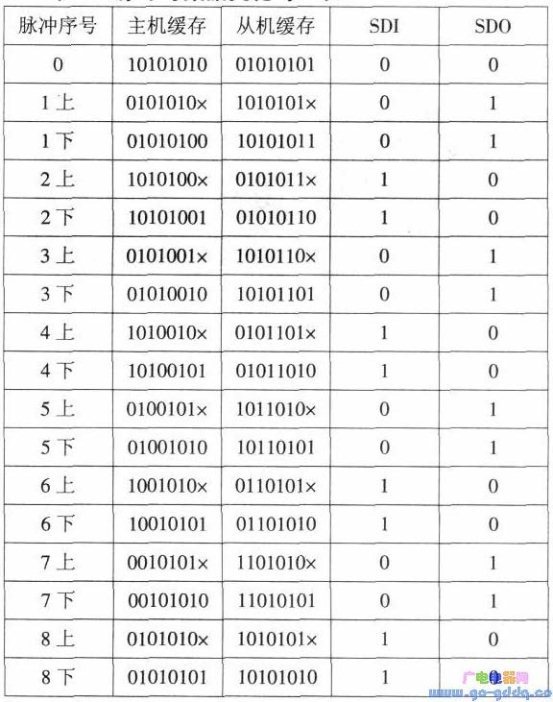

���O(sh��)���C(j��)�͏ęC(j��)��ʼ���;w���������C(j��)�� sbuff=0xaa���ęC(j��)�� sbuff=0x55�����挢�ֲ� �� SPI �� 8 ���r����ڵĔ�(sh��)��(j��)��r��ʾһ�飺���O(sh��)�����ذl(f��)�͔�(sh��)��(j��)���@�Ӿ�����˃ɂ��Ĵ� �� 8 λ�Ľ��Q��������ϱ�ʾ�����ء��±�ʾ�½��أ�SDI��SDO ���������C(j��)���Եġ�

SPI��(sh��)��(j��)�l(f��)���c���ՙC(j��)��.pdf

(341.3 KB, ���d��(sh��): 61)

SPI��(sh��)��(j��)�l(f��)���c���ՙC(j��)��.pdf

(341.3 KB, ���d��(sh��): 61)

| �gӭ���R (http://www.raoushi.com/bbs/) | Powered by Discuz! X3.1 |