FPGA對于輸入的信號一般都要經過消抖處理,以消除干擾信號。對于兩個設備之間的數據傳輸,這一點顯得尤為重要。

消抖一般通過記錄脈沖的個數,對輸入信號的尖峰寬度進行限制,達不到預定的寬度,即認為是干擾,必須加以濾除,部分代碼如下。因此,信號經過消抖去除干擾信號以后,必然產生延遲,延遲時間與系統晶振頻率以及計數脈沖個數有關。

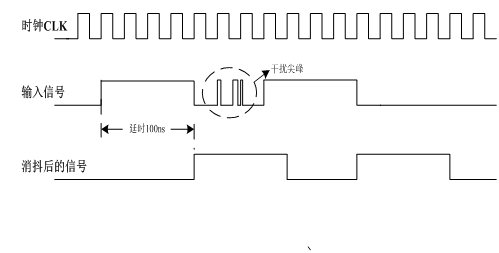

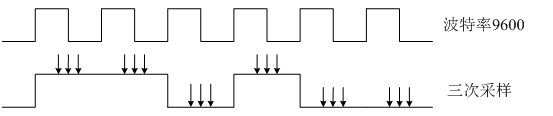

例如:設系統晶振為40MHz,消抖時間為4個CLK,一個脈沖時間為1/40M=25ns,所以信號延時為25*4=100ns,如圖1所示。

圖1 信號消抖示意圖

代碼示例:

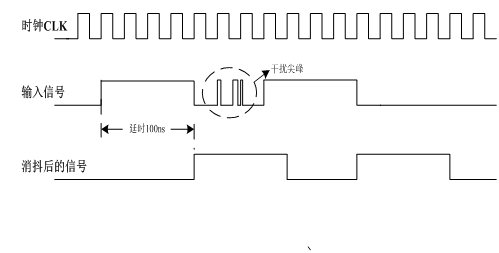

(a)延時4clk

仿真結果如圖2:

圖2消抖程序仿真圖

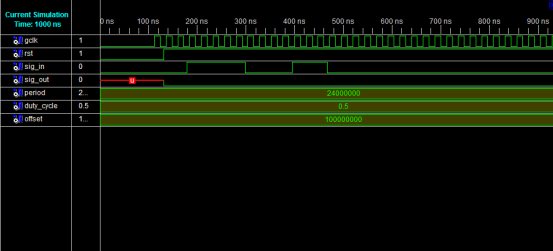

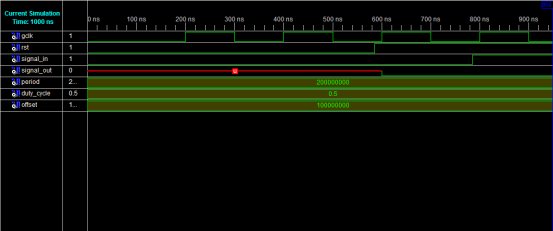

(b) 延時4ms

仿真結果;

圖3延時仿真圖

現通過設計一個可以實現8.5分頻,等占空比的17分頻,2、4、8、16、32分頻,及占空比為1∶8和4∶5的9分頻等多種形式分頻的分頻器。分頻器由帶使能端的異或門、模N計數器和一個2分頻器組成,本設計用D觸發器來完成2分頻的功能,實現方法是:將觸發器的Q反輸出端反饋回輸入端D,將計數器的一個計數輸出端作為D觸發器的時鐘輸入端。各功能模塊的VHDL語言實現如下。

1).模N計數器的實現

一般設計中用到計數器時,我們可以調用lpm庫中的計數器模塊,也可以采用VHDL語言自己設計一個模N計數器。本設計采用VHDL語言設計一個最大模值為16的計數器。輸入端口為:使能信號en,復位信號clr和時鐘信號clk;輸出端口為:qa、qb、qc、qd。其VHDL語言描述略。

2).帶使能控制的異或門的實現

輸入端為:xor_en:異或使能,a和b:異或輸入;輸出端為:c:異或輸出。當xor_en為高電平時,c輸出a和b的異或值。當xor_en為低電平時,c輸出信號b。其VHDL語言略。

3).分頻(觸發器)的實現

輸入端為:時鐘信號clk,輸入信號d;輸出端為:q:輸出信號a,q1:輸出信號a反。其VHDL語言略。

以下是幾種分頻器的分析:

偶數分頻器

頻最易于實現,欲實現占空比為50%的偶數N分頻,一般來說有兩種方案:,分頻器的基礎是計數器,設計分頻偶數分N/2-1時,將輸出電平進行一次翻轉,同時給計數器一個復位信號,如此循環下去;二是當計數器輸出為0到N/2-1時,時鐘輸出為0或1,計數器輸出為N/2到N-1時,時鐘輸出為0或1,計數器輸出為N/2到N-1時,時鐘輸出為0或1,計數器輸出為N-1時,復位計數器,如此循環下去。

實現非50%占空比的奇數分頻,如占空比為20%、40%、60%、80%的5分頻器,可以采用類似偶數分頻的第二種方案;但如果實現占空比為50%的奇數分頻,就不能使用偶數分頻中所采用的方案了。

下面就以實現占空比40%的5分頻分頻器為例,說明非50%占空比的奇數分頻器的實現。該分頻器的實現對于我們實現50%占空比的分頻器有一定的借鑒意義。一下是奇數分頻仿真結果圖。

半整數分頻器

僅僅采用數字分頻,不可能獲得占空比為50%的N+0.5分頻,我們只可以設計出占空比為(M+0.5)/(N+0.5)或者M/(N+0.5)的分頻器,M小于N。這種半整數分頻方法是對輸入時鐘進行操作,讓計數器計數到某一個數值時,將輸入時鐘電平進行一次反轉,這樣,該計數值只保持了半個時鐘周期,因此實現半整數分頻。

如上所述,占空比為50%的奇數分頻可以幫助我們實現半整數分頻,將占空比為50%的奇數分頻與待分頻時鐘異或得到計數脈沖,下面的代碼就是依靠占空比為50%的5分頻實現2.5分頻器的。仿真結果如圖所示。

小數分頻器

小數分頻是通過可變分頻和多次平均的方法實現的。例如要實現4.7分頻,只要在10次分頻中,做7次5分頻,3次4分頻就可以得到。再如要實現5.67分頻,只要在100次分頻中,做67 6分頻,33次5分頻即可。考慮到小數分頻器要進行多次兩種頻率的分頻,必須設法將兩種分頻均勻。表1以2.7分頻為例,小數部分進行累加,如果大于等于10,則進行3分頻,如果小于10,進行2分頻。

仿真波形如圖 所示,我們可以清楚的看到2.7分頻的實現。按照占空比的定義,該分頻器的占空比應為10/27。

分數分頻器

將小數分頻的方法進行擴展,可以得到形如M*(L/N) 的分數分頻的方法,例如,2*(7/13)等于分母的,進行分頻,只要在13次分頻中,進行7次3分頻,6次2分頻就可以得到。同樣,為了將兩種分頻均勻,將分子部分累加,小于分母的,進行M分頻,大于(M+1)分頻。表2顯示了2*(7/13) 的分頻次序。

仿真波形如圖11所示。顯然,該分頻器的占空比為13/33。

積分分頻器用于實現形如![]() 的分頻,例如8/3分頻。我們當然可以使用上面提到的分數分頻的方法,但對于這種形式的分頻,使用積分分頻的方法綜合往往占用更少的FPGA資源。

的分頻,例如8/3分頻。我們當然可以使用上面提到的分數分頻的方法,但對于這種形式的分頻,使用積分分頻的方法綜合往往占用更少的FPGA資源。

積分分頻法基于下述原理:一個m位的二進制數字每次累加N,假定累加x次累加值最低m位回到0,同時超過![]() 次,那么,當前累加的數字應該是

次,那么,當前累加的數字應該是![]() ;每越過

;每越過![]() 一次,最高位變化 2 次,所以,累加 x 次,最高位變化 2y次,得到

一次,最高位變化 2 次,所以,累加 x 次,最高位變化 2y次,得到![]() 分頻的分頻器,例如,取m為4,N為3,當累加16次時,累加值為48,最低m位變回到0,同時越過16三次,最高位變化6次,由此得到16/6=8/3分頻的分頻器。

分頻的分頻器,例如,取m為4,N為3,當累加16次時,累加值為48,最低m位變回到0,同時越過16三次,最高位變化6次,由此得到16/6=8/3分頻的分頻器。

分頻仿真結果如圖所示。

異步串行數據傳輸具有設計簡單、傳輸穩定等優點。其兩個主要參數是波特率和數據位格式。數據位格式又稱幀格式,一般包含一個起始位(邏輯0),一個終止位(邏輯1)以及校驗位。在發送空閑時,總線一般處于邏輯1狀態。這樣當接收端檢測到總線上由高到低的電平跳變,即認為是數據開始傳輸。波特率是用來約定通信雙方的通信速率,一般通過對系統時鐘進行分頻來實現,RS-232協議中,常用的波特率有115200、9600等,RS-422與RS-232原理基本相同,只是在傳輸線路上,為了抗干擾,采用了差分方式。

在FPGA應用領域 ,串行數據傳輸一般采用422總線。通過對系統晶振分頻,得到對應的波特率,比如對40MHz經行4分頻,得到10MBit的傳輸速率。解碼端會根據預先設定的波特率,對時鐘進行分頻,每隔相等時間讀取總線上的一位數據。流程如下:在檢測到起始位低電平之后,接收端(即解碼端)每隔一位時間,采集總線上的電平,并寫入移位寄存器中,直到將一幀數據全部接收,然后判斷校驗位,如果正確,則接收、編幀,否則,丟棄。

由于受溫度等因素的影響,晶振會產生誤差,串行數據在傳輸過程中,可能會受到干擾而產生毛刺。所以在一些對數據準確度要求比較高的場合,就得考慮串行數據傳輸的容錯能力。對于這種情況,第一種方法通常會采取對總線上的一位分別采集三次,比較得到的三個電平,進而得到該位可信度更高的值,如圖2所示;第二種方法則會將電平的采集點放在每一位的靠近中間的位置,通過計算晶振的最大誤差,則可以計算出系統的最大容錯能力。設晶振誤差5%,頻率為40MHz,1/40MHz=25ns,25*0.05=1.25ns,設波特率為4Mbit/s,所以對于40bit一幀的串行數據,累積誤差最大會有1.25*40*4*50%=100ns,而比特位寬只有100ns,所以有可能會發生錯位。

圖11 多次采樣減小誤差示意圖

圖11 多次采樣減小誤差示意圖

部分代碼如下

(a)422串行發送

仿真結果:

圖12異步串行通信的發送與接收

PCM脈沖編碼調制是將模擬信號轉換成二進制數字信號的編碼過程。在無線遙測系統中,遙測采編器對多路模擬信號通過特定的順序(幀結構)進行模數轉換采樣,然后再將采得的PCM碼并串轉換,串行送至無線發射機發射。地面站通過無線接收機接收。解碼后的PCM碼是一個由二進制數構成的串行序列。地面接收設備的主要任務是將串行PCM碼中的數據解調出來,這就需要根據PCM碼流中特定的同步碼確定數據的起始位,在位信號變化時的上升沿(或下降沿)把PCM碼流的位同步信號分離出來,再通過串行數據到并行數據的轉換把數據并行輸出。

PCM碼的串并轉換分為三步,第一步是提取同步信號,第二步是提取幀同步信號,第三步是根據已得到的位同步和幀同步完成字同步和串并轉換。

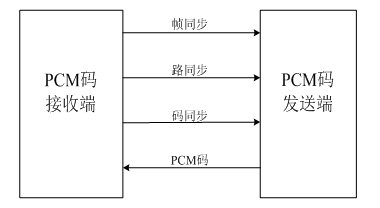

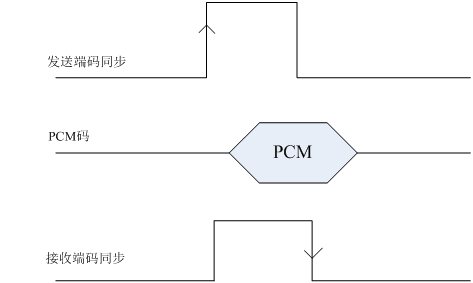

PCM碼在發送以及接收(解碼)過程中,都會用幀同步和碼同步對PCM碼進行同步,有些還會用到路同步信號,如圖13所示。一般是PCM碼接收端發送同步信號(即幀同步、碼同步和路同步)。PCM碼發送端根據接收到的同步信號輸出PCM碼,比如在碼同步的上升沿或者下降沿給出數據,接收端則根據自己發出的同步信號接收PCM碼。在實際數據傳輸過程中,考慮到信號的延時,一般發送端在碼同步上升沿給出PCM數據,接收端在碼同步下降沿讀取PCM數據,而幀同步一般用作幀復位,路同步用作字節復位,如圖14所示。

接收端接收到PCM數據后,一般要經過編幀,加上幀頭、幀尾以及幀計數,然后上傳給計算機。計算機則將數據解包,提取出有用的信息。

圖13 PCM碼接收發送過程中的信號示意圖

圖14 同步信號示意圖

部分參考代碼:

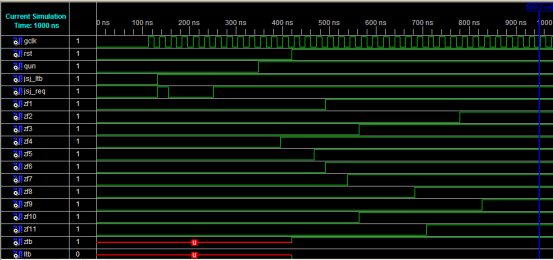

(a)幀同步、路同步、碼同步信號的產生

仿真結果:

圖15PCM通信的發送與接收仿真圖

VHDL信號消抖.doc

(749.5 KB, 下載次數: 10)

VHDL信號消抖.doc

(749.5 KB, 下載次數: 10)

| 歡迎光臨 (http://www.raoushi.com/bbs/) | Powered by Discuz! X3.1 |