標題: EAD萬年歷實訓報告及Verilog HDL源碼 [打印本頁]

作者: time123456 時間: 2018-5-14 17:47

標題: EAD萬年歷實訓報告及Verilog HDL源碼

《EDA技術及應用》實訓報告

1 系統設

1.1 設計要求

1.1.1 設計任務

設計并制作一臺數字日歷。

1.1.2 性能指標要求

⑴用Verilog HDL語言設計一個數字日歷。

⑵數字日歷能顯示年、月、日、時、分和秒。

⑶通過開關分別控制對年、月、日或時、分、秒校對及自動切換、,并且

運用按鈕對年、月、日或時、分、秒校對。

⑷通過按鈕對數碼管全部清零。

1.2 設計思路及設計框圖

1.2.1設計思路

通過EDA課程的學習,可知運用Verilog HDL語言設計一個數字日歷

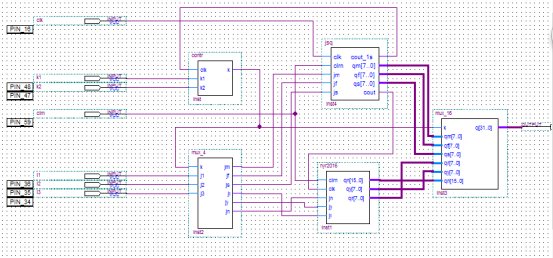

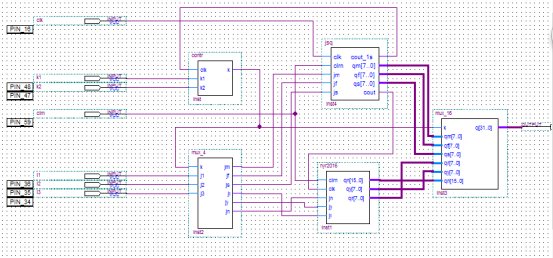

括計時器模塊(jsq60、jsq)、年月日模塊(nyr2016)、控制模塊(contr)、

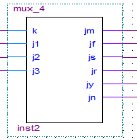

校時選擇模塊(mux_4)、顯示選擇模塊(mux_16);然后將各個模塊連接起來畫成原理圖再下載到實訓儀上,調節開關及按鈕來實現數字日歷的功能。

1.2.2總體設計框圖

2 各個模塊程序的設計

地電平,用于萬年歷的自動倒換的顯 ⑴使用了一個16分頻的電路,輸出rc是周期為16秒的方波,即8秒高電平、8秒示模式。

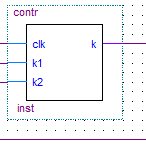

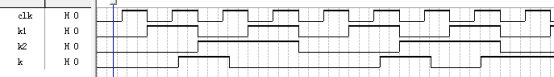

分析:如圖所示,其中,clk是1秒時鐘輸入端,k1和k2是控制輸入端,當k1k2=00或11時是自動顯示模式,控制數碼顯示器用8秒鐘時間顯示年、月、日,另外8秒時鐘時間顯示時、分、秒;當k1k2=01時,僅顯示年、月、日,同時用j1,j2,和j3校秒、校分、校時;當k1k2=10時,僅顯示年、月、日,同時用j1、j2和j3校日、校月和校年;k是控制輸出端。

⑵分別設計一個能顯示年月日和時分秒的程序

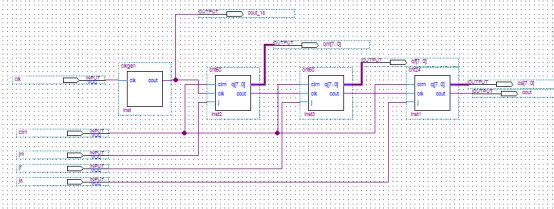

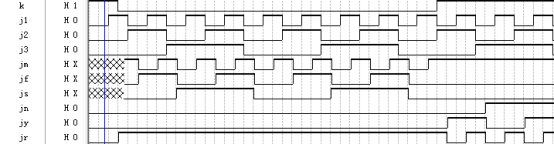

校準年月日和秒分時的原理圖如下:

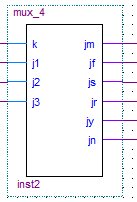

分析:①當k=0時,開關j1,j2,j3校秒時分然后將信號分別送到jsq模塊的jm(校秒)、jf(校分)、js(校時)。

②當k=1時,開關j1,j2,j3校年月日然后將信號分別送到nyr2009模塊的jr(校日)、jy(校月)、jn(校年)。

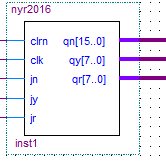

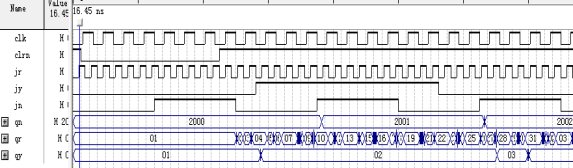

計算年月日的模塊如下:

分析:clrn是異步清除輸入端,低電平有效;clk是時鐘輸入端,上升沿有效;jn、jy和jr分別是校年、校月、校日輸入端;qn[15..0]、qy[7..0]、qr[7..0]分別是年、月、日的輸出端。

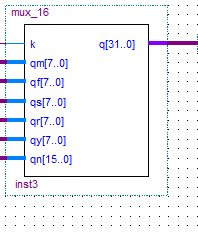

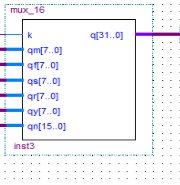

顯示時分秒與年月歷的模塊如下:

分析:①當k=0時,把jsq送來的時分秒的狀態信號送到數碼管顯示。

②當k=1時,把nyr2016送來的年月日的狀態信號送到數碼管顯示。

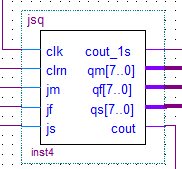

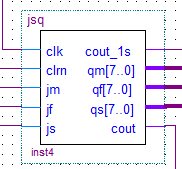

計算時分秒的模塊如下:

分析: clrn是異步清除輸入端,低電平有效;clk是時鐘輸入端,上升沿有效;jm、jf和js分別是校秒、校分、校時輸入端;qm[7..0]、qf[7..0]、qs[7..0]分別是年、月、日的輸出端;cout是進位;clkcout是由clk控制的秒秒脈沖。

⑶計時器24的模塊如下:

3 調試過程

在這一次實訓中我選擇的是數字日歷電路的設計。首先按照實訓題目的要求進行電路的設計,編寫好程序畫好原理圖;然后用Quartus9.0進行程序的調試和修改,看看那些地方有錯誤就把錯誤的地方改正;最后來到實驗室下載到試驗箱進行題目要求的驗證和調試。

4 功能測試

4.1 測試儀器與設備

EDA實訓儀的I/O設備 1臺

4.2 性能指標測試

⑴數字日歷能夠顯示年、月、日、時、分和秒。

⑵用EDA實訓儀上的8只八段數碼管分兩屏分別顯示年、月、日和時、分、秒,即在一定時間段內顯示年、月、日,然后在另一時間段內顯示時、分、秒,兩個時間段能自動倒換。

⑶數字日歷具有復位和校準年、月、日、時、分、秒的按鈕,但校年和校時同用一個按鈕,即在顯示年、月、日時用此按鈕校年,在顯示時、分、秒時則用此按鈕校時。

4.3 誤差分析

無須誤差分析

5 實訓心得體會

這次實訓,做的是萬年歷,在上課上的是剛好做過,覺得挺簡單的,覺得挺放松,不過為了與老師在上課上做得不同,就小小的設計一個亮燈功能。不過真正做起來的時候發現了很多問題,因為上課的時候匆匆忙忙的完成萬年歷,當時對程序還不是很熟悉,要看書了解各條語句,對操作也不是太熟悉,要請教同學,但最終還是完成了,不過在驗收的時候不能全部回答老師提出的問題,說明在EDA道路上還有走很長的道路。努力加油吧。通過這次EDA實訓,我學會并熟悉運用quartus軟件,非常感謝黃金海老師的耐心指導

6 參考文獻

EDA技術與應用/江國強編著.——4版.電子工業出版社,2013。

附錄

附錄1:仿真波形圖(部分模塊)

cnt60模塊仿真波形圖

contr模塊仿真波形圖

mux-4模塊仿真波形圖

nyr2016模塊仿真波形圖

附錄2:程序清單

⑴基于Verilog HDL的控制模塊contr

module contr(clk,k1,k2,k);

input clk,k1,k2;

output reg k;

reg [3:0] qc;

reg rc;

always @(posedge clk)

begin qc=qc+1;

if (qc<8) rc=0;

else rc=1;

case ({k1,k2})

0:k=rc;

1:k=0;

2:k=1;

3:k=rc;

endcase

end

endmodule

⑵基于Verilog HDL的校時選擇模塊mux_4

module mux_4(k,jm,jf,js,jr,jy,jn,j1,j2,j3);

input k,j1,j2,j3;

output reg jm,jf,js,jr,jy,jn;

always

begin

if (k==0) {jm,jf,js}={j1,j2,j3};

else {jr,jy,jn}={j1,j2,j3};

end

endmodule

⑶基于Verilog HDL的顯示模塊mux_16

module mux_16(k,qm,qf,qs,qr,qy,qn,q);

input k;

input[7:0] qm,qf,qs,qr,qy;

input[15:0] qn;

output reg [31:0] q;

always

begin

if (k==0) begin

q[31:24]=0;

q[23:0]={qs,qf,qm};end

else q={qn,qy,qr};

end

endmodule

⑷基于Verilog HDL的年月日模塊nyr2016

module nyr2016(clrn,clk,jn,jy,jr,qn,qy,qr);

input clrn,clk,jn,jy,jr;

output [15:0] qn; //年為4位有效數字,要16位顯,賦值

output [7:0] qy,qr; //月和日為2位有效數字,8位顯示

reg [15:0] qn;

reg [7:0] qy,qr;

reg clkn,clky;//日的進位和月的進位

reg [7:0] date;//日的中間變量年

reg clkn1,clkn2,clkn3;//的個、十、百位的進位

initial begin clkn1=1;clkn2=1;clkn3=1;end//初始化程序

initial begin qn='h2000;qy=1;qr=1;end

always @(posedge (clk^jr) or negedge clrn)//校日程序

begin

if (~clrn) qr=1;

else begin

if (qr==date) qr=1;//每個月的天數不同,所以賦值的data不一樣

else qr=qr+1;

if (qr[3:0]=='ha) begin

qr[3:0]=0; qr[7:4]=qr[7:4]+1;end

if (qr==date) clky = 1;

else clky = 0;end

end

always @(posedge clky^jy or negedge clrn)//月程序

begin

if (~clrn) qy=1;

else begin

if (qy=='h12) qy=1;

else qy=qy+1;

if (qy[3:0]=='ha) begin

qy[3:0]=0;qy[7:4]=qy[7:4]+1;end

if (qy=='h12) clkn = 1;

else clkn = 0;end

end

always

begin

case (qy)//不同月的天數選擇

'h01: date='h31;

'h02: begin

if ((qn%4==0)&(qn%100 != 0)|(qn%400==0)) date='h29;

else date='h28; end//閏年和非閏年二月的天數判斷

'h03: date='h31;

'h04: date='h30;

'h05: date='h31;

'h06: date='h30;

'h07: date='h31;

'h08: date='h31;

'h09: date='h30;

'h10: date='h31;

'h11: date='h30;

'h12: date='h31;

default :date='h30;

endcase

end

always @(posedge (clkn^jn) or negedge clrn )//年程序

begin

if (~clrn) qn[3:0]=0;//個位進位程序

else begin if(qn[3:0]==9) qn[3:0]=0;

else qn[3:0]=qn[3:0]+1;

if (qn[3:0]==9) clkn1=0;

else clkn1=1;end

end

always @(posedge clkn1 or negedge clrn )

begin

if (~clrn) qn[7:4]=0;//十位進位程序

else begin if(qn[7:4]==9) qn[7:4]=0;

else qn[7:4]=qn[7:4]+1;

if (qn[7:4]==9) clkn2=0;

else clkn2=1;end

end

always @(posedge clkn2 or negedge clrn )

begin

if (~clrn) qn[11:8]=0;//百位進位程序

else begin if(qn[11:8]==9) qn[11:8]=0;

else qn[11:8]=qn[11:8]+1;

if (qn[7:4]==9) clkn3=0;

else clkn3=1;end

end

always @(posedge clkn3 or negedge clrn )//年程序顯示程序

begin

if (~clrn) qn[15:12]=2;

else if(qn[15:12]==9) qn[15:12]=0;

else qn[15:12]=qn[15:12]+1;

end

endmodule

⑸基于Verilog HDL計數器jsp

0.jpg (24.65 KB, 下載次數: 71)

下載附件

2018-5-15 01:05 上傳

0.png (45.28 KB, 下載次數: 54)

下載附件

2018-5-15 01:05 上傳

全部資料51hei下載地址:

EDA萬年歷.rar

(1.2 MB, 下載次數: 134)

EDA萬年歷.rar

(1.2 MB, 下載次數: 134)

2018-5-14 17:46 上傳

點擊文件名下載附件

下載積分: 黑幣 -5

作者: Josie 時間: 2018-11-29 22:45

請教那個計時器模塊怎么設計?

| 歡迎光臨 (http://www.raoushi.com/bbs/) |

Powered by Discuz! X3.1 |

EDA萬年歷.rar

(1.2 MB, 下載次數: 134)

EDA萬年歷.rar

(1.2 MB, 下載次數: 134)