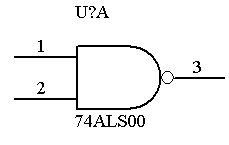

A | B | y |

0 | 0 | |

0 | 1 | |

1 | 0 | |

1 | 1 |

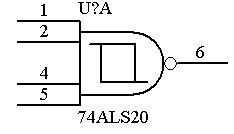

A | B | C | D | Y |

0 | X | X | X | |

X | 0 | X | X | |

X | X | 0 | X | |

X | X | X | 0 | |

1 | 1 | 1 | 1 |

本次 實(shí)驗(yàn) 成績(jī) | 項(xiàng)目及比例 | 實(shí)驗(yàn)操作 (50%) | 報(bào)告書寫 (30%) | 出勤和課堂紀(jì)律 (10%) | 課堂提問(wèn) (10%) | |

得分 | ||||||

成績(jī)合計(jì) | ||||||

教師簽字: | 批改日期: | |||||

本次 實(shí)驗(yàn) 成績(jī) | 項(xiàng)目及比例 | 實(shí)驗(yàn)操作 (50%) | 報(bào)告書寫 (30%) | 出勤和課堂紀(jì)律 (10%) | 課堂提問(wèn) (10%) | |

得分 | ||||||

成績(jī)合計(jì) | ||||||

教師簽字: | 批改日期: | |||||

一、實(shí)驗(yàn)?zāi)康?/font>

1、熟悉中規(guī)模集成計(jì)數(shù)器的邏輯功能及使用方法

2、掌握用74LS161構(gòu)成幾種進(jìn)制計(jì)數(shù)器的方法

3、熟悉中規(guī)模集成計(jì)數(shù)器各輸出波形及應(yīng)用

二、實(shí)驗(yàn)原理

計(jì)數(shù)器是典型的時(shí)序邏輯電路,它是用來(lái)累計(jì)和記憶輸入脈沖的個(gè)數(shù).計(jì)數(shù)是數(shù)字系統(tǒng)中很重要的基本操作,集成計(jì)數(shù)器是最廣泛應(yīng)用的邏輯部件之一。計(jì)數(shù)器種類較多,按構(gòu)成計(jì)數(shù)器中的多觸發(fā)器是否使用一個(gè)時(shí)鐘脈沖源來(lái)分,有同步計(jì)數(shù)器和異步計(jì)數(shù)器;根據(jù)計(jì)數(shù)制的不同,可分為二進(jìn)制計(jì)數(shù)器、十進(jìn)制計(jì)數(shù)器和任意進(jìn)制計(jì)數(shù)器;根據(jù)計(jì)數(shù)的增減趨勢(shì),又分為加法、減法和可逆計(jì)數(shù)器。還有可預(yù)置數(shù)和可編程序功能計(jì)數(shù)器等。本實(shí)驗(yàn)主要研究中規(guī)模十進(jìn)制計(jì)數(shù)器74LS161的功能及應(yīng)用。

2、中規(guī)模集成計(jì)數(shù)器

74LS161 是四位二進(jìn)制可預(yù)置同步計(jì)數(shù)器,由于它采用4 個(gè)主從JK 觸發(fā)器作為記憶單元,故又稱為四位二進(jìn)制同步計(jì)數(shù)器,其集成芯片管腳如圖所示:

管腳符號(hào)說(shuō)明:電源正端Vcc,接+5V ;異步置零(復(fù)位)端Rd;時(shí)鐘脈沖CP;預(yù)置數(shù)控制端 A、B、C、D;數(shù)據(jù)輸出端 QA、QB、QC、QD;進(jìn)位輸出端 RCO:使能端EP,ET;預(yù)置端 ![]() ;

;

圖3.8.2 74LS161 管腳圖

該計(jì)數(shù)器由于內(nèi)部采用了快速進(jìn)位電路,所以具有較高的計(jì)數(shù)速度。各觸發(fā)器翻轉(zhuǎn)是靠時(shí)鐘脈沖信號(hào)的正跳變上升沿來(lái)完成的。時(shí)鐘脈沖每正跳變一次,計(jì)數(shù)器內(nèi)各觸發(fā)器就同時(shí)翻轉(zhuǎn)一次,74LS161的功能表如表所示:

表74LS161 邏輯功能表

表74LS161 邏輯功能表

3、計(jì)數(shù)器的級(jí)聯(lián)使用

若所要求的進(jìn)制已超過(guò)16,則可通過(guò)幾個(gè)74LS161 進(jìn)行級(jí)聯(lián)來(lái)實(shí)現(xiàn),在滿足計(jì)數(shù)條件的情況下有如下方法:

1) 同步聯(lián)接法:

CP 是共同的,只是把第一級(jí)的進(jìn)位輸出RCO 接到下一級(jí)的ET 端即可,平時(shí)RCO=0 則計(jì)數(shù)器2 不能工作,當(dāng)?shù)谝患?jí)計(jì)滿時(shí),RCO=1,最后一個(gè)CP 使計(jì)數(shù)器1 清零,同時(shí)計(jì)數(shù)器2 計(jì)一個(gè)數(shù),這種接法速度不快,不論多少級(jí)相聯(lián),CP 的脈寬只要大于每一級(jí)計(jì)數(shù)器延遲時(shí)間即可。其框圖如圖:

2) 異步聯(lián)接法:

把第一級(jí)的進(jìn)位輸出端RCO 接到下一級(jí)的CP 端,平時(shí)RCO=0 則計(jì)數(shù)器2 因沒(méi)有計(jì)數(shù)脈沖而不能工作,當(dāng)?shù)谝患?jí)計(jì)滿時(shí),RCO=1,計(jì)數(shù)器2 產(chǎn)生第一個(gè)脈沖,開(kāi)始計(jì)第1 個(gè)數(shù),這種接法速度慢,若多級(jí)相聯(lián),其總的計(jì)數(shù)時(shí)間為各個(gè)計(jì)數(shù)器延遲時(shí)間之和。其框圖如圖所示

4、實(shí)現(xiàn)任意進(jìn)制計(jì)數(shù)器 由于74LS161的計(jì)數(shù)容量為16,即計(jì)16個(gè)脈沖,發(fā)生一次進(jìn)位,所以可以用它構(gòu)成16進(jìn)制以內(nèi)的各進(jìn)制計(jì)數(shù)器,實(shí)現(xiàn)的方法有兩種:置零法(復(fù)位法)和置數(shù)法(置位法)。

(1) 用復(fù)位法獲得任意進(jìn)制計(jì)數(shù)器 假定已有N進(jìn)制計(jì)數(shù)器,而需要得到一個(gè)M進(jìn)制計(jì)數(shù)器時(shí),只要M<N,用復(fù)位法使計(jì)數(shù)器計(jì)數(shù)到M時(shí)置“0”,即獲得M進(jìn)制計(jì)數(shù)器。

(2) 利用預(yù)置功能獲M進(jìn)制計(jì)數(shù)器 置位法與置零法不同,它是通過(guò)給計(jì)數(shù)器重復(fù)置入某個(gè)數(shù)值的的跳越N-M個(gè)狀態(tài),從而獲得M進(jìn)制計(jì)數(shù)器的,如圖所法。置數(shù)操作可以在電路的任何一個(gè)狀態(tài)下進(jìn)行。這種方法適用于有預(yù)置功能的計(jì)數(shù)器電路。圖上述二種方法的原理示意圖

(a) (b)

例如:利用兩片十進(jìn)制計(jì)數(shù)器74LS161接成35進(jìn)制計(jì)數(shù)器?

本例可以采用整體置零方式進(jìn)行。首先將兩片74LS161以同步級(jí)聯(lián)的方式接成16×16=256進(jìn)制的計(jì)數(shù)器。當(dāng)計(jì)數(shù)器從全0狀態(tài)開(kāi)始計(jì)數(shù)時(shí),計(jì)入了35個(gè)脈沖時(shí),經(jīng)門電路譯碼產(chǎn)生一個(gè)低電平信號(hào)立刻將兩片74LS161同時(shí)置零,于是便得到了35進(jìn)制計(jì)數(shù)器。電路連接圖如圖所示

二片74LS161構(gòu)成35進(jìn)制計(jì)數(shù)器電路連接圖

三、實(shí)驗(yàn)內(nèi)容與步驟

1、測(cè)試74LS161的邏輯功能。

1) 分別畫出置零法、置數(shù)法的電路連接圖,用點(diǎn)脈沖CP,觀察計(jì)數(shù)狀態(tài),畫出狀態(tài)轉(zhuǎn)換圖

2)在CP端加入連續(xù)脈沖信號(hào),用示波器觀察輸出波形,并將QA、QB、QC、QD的波形圖繪在下圖中

Qa

Qb

Qc

Qd

2016數(shù)字電路技術(shù)實(shí)驗(yàn)指導(dǎo)書-.doc

(272.62 KB, 下載次數(shù): 5)

2016數(shù)字電路技術(shù)實(shí)驗(yàn)指導(dǎo)書-.doc

(272.62 KB, 下載次數(shù): 5)

| 歡迎光臨 (http://www.raoushi.com/bbs/) | Powered by Discuz! X3.1 |