���}: Verilog HDLͬ��FIFO���OӋ��� [��ӡ���]

����: YUQIAN123 �r�g: 2018-4-2 13:08

���}: Verilog HDLͬ��FIFO���OӋ���

����һ��fifo�OӋ�����������V�Z��

��W���W���̌WԺ

Verilog HDL�Ŀ�OӋ���

�}Ŀͬ��FIFO���OӋ

���I������W̖늿�1362910201 13629102225

���n��̖6292758

ժҪ

FIFO��1����First Input First Output�Ŀs�����������M�ȳ������������@��һ�N���y�İ�����з��������Ҳ��һ�N���M�ȳ��Ĕ���������������c��ͨ�惦���ą^�e�Ǜ]���ⲿ�x����ַ�������@��ʹ�������dz����Σ���ȱ�c����ֻ������딵��������x������������䔵����ַ�ɃȲ��x��ָ��ԄӼ�1��ɣ���������ͨ�惦���ǘӣ������ɵ�ַ���Q���xȡ����ij��ָ���ĵ�ַ�������������Ч�ʺͽ���ϵ�y�OӋ���y������������ʹ��Verilog HDL�� 2 �������Z�������ͨ�^Xilinx��˾��ISE ��3��ܛ���M�г����Լ�����������ٌ���������MBasys2�_�l����������OӋ���F��һ�N4bit-256���ͬ��FIFO����ṩ�������_��

�P�I�~��ͬ��FIFO Verilog HDL Basys

Abstract

FIFO is a acronym of First Input First Output, FIFO queue, which is a traditional sequential execution method, but also a FIFO data register. It differs from the ordinary that there is no external memory write address lines, so very simple to use, but the disadvantage is that the only sequential write data sequentially read out, the data read by the internal address pointer is automatically incremented by 1 to complete, not like generic memory that can be determined by the address line read from or written to a specified address. In order to improve efficiency and reduce the difficulty of system design, we use Verilog HDL description language, take advantage of Xilinx's ISE software programming and simulation, and then burn program written Basys2 development board, designed and implemented a 4bit-256 deep synchronous FIFO, provide data buffering.

Keywords: synchronous FIFO Verilog HDL Basys2

Ŀ�

һ������ϵ�y�OӋ

1.1 �OӋĿ��

1.2 �����Č��ȷ����c�_��

1.2.1 ��ʼ����

1.2.2 ���M����

1.3 �·����D���f��

1.4 �·�OӋ���f��

1.4.1 플�ģ�K

1.4.2 �r犷��lģ�K

1.4.3 ����ݔ��ݔ��ģ�K

1.4.4 �g�aģ�K

��������Y���cӑՓ

2.1 �{ԇ���E�c�F��

2.1.1 �{ԇ����

2.1.2 ����

2.1.3 ��������Basys2�_�l��

2.2 ���F���}�c����

2.3 �����P�����ķ����cӑՓ

������ĵ��w��

3.1 �OӋ���c

3.2 �u���Y��

3.3 ���ƽ��h

3.4 �����w��

��������������īI

���������

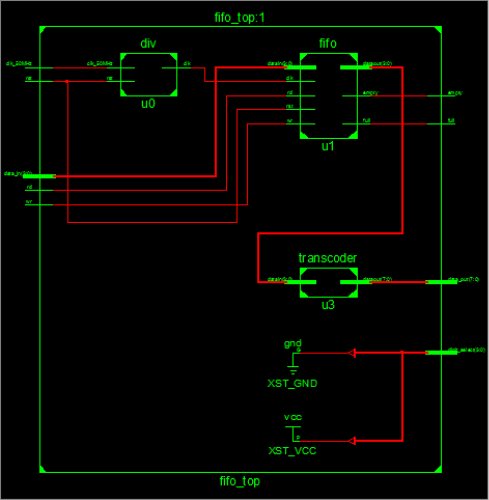

���һ RTLԭ��D

��䛶� ��Ʒ�DƬ

һ��ϵ�y�OӋ

1.1 �OӋĿ��

����얹̺ͼ����VerilogHDL�����OӋ�c�C�ϡ��c��������Ӽ��g�����T�n�̵���Փ֪�R��������������˽����ʹ��VerilogHDL�Z���M���·�OӋ�IJ��E�c�����������ISEܛ�������Լ������ʹ�÷��������������˽�Basys2�_�l���ʹ�÷�����ͬ�r�҂�������·�OӋ���Mһ�����J�R��������҂����ڌ��OӋ�c�����ČW���춨�˻��A��

1.2 �����Č��ȷ����c�_��

1.2.1 ��ʼ����

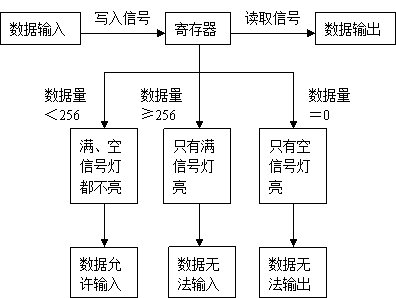

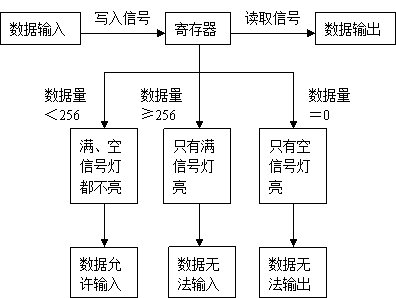

ʹ��100kHz���鹤���r犡���������̖��Ч�r����ÿ���r��������R�����������һ����������ͬ�r�Ĵ���ָ�ָ��Ĵ�����һλ�����xȡ��̖��Ч�r��ÿ��ʼ�K�������R���x��һ����������������M�����M��̖���������o�����r������̖������

ȱ�c��ԓ�����ij������MBasys2�_�l��������ݔ�딵���кܸߵ�Ҫ����������ٶȱ�횺ܿ�����������ÿһ���������R�͕�����һ�����������������ݔ�벻���r��ͬһ����������ݔ��ɱ��������x���ٶ�̫�죬�G���ʸ�������

���c��ԓ�����m���ڷ�����������Կ��ٌ��F���ܷ������

1.2.2 ���M����

ͬ��ʹ��100kHz���鹤���r���������ʹ���_�P�O�ú�4λҪ����Ĕ����������밴�I��ԓ��������Ĵ����������S�r�ɰ����xȡ���I������x��һ���������@ʾ�ڔ��a�������������M��������M��̖������������o�����r�������̖�����������

ȱ�c��ԓ��������r�g�����^�L�������

���c��ԓ�����ij������MBasys2�_�l�������S�r���Ԍ��딵����ͬ�r�����S�r�x�������������ٶ�����������Ŀǰ�yԇ�G���ʞ����������

1.3 �·����D���f��

1.4 �·�OӋ���f��

1.4.1 플�ģ�K

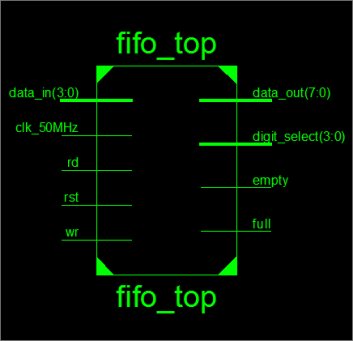

�B�ӿ��ƕr犷��lģ�Kdiv�����������ݔ��ݔ��ģ�Kfifo���g�aģ�Ktranscoder

1.4.2 �r犷��lģ�K

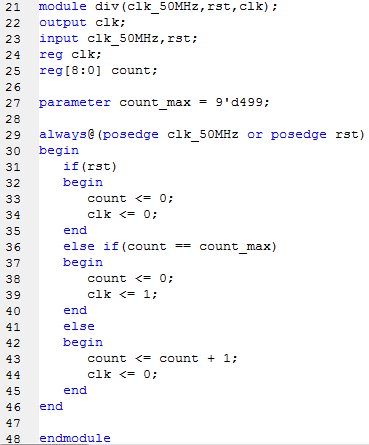

��Basys2�_�l���ϵ�50MHz�r�ݔ����l��100kHz��������ģ�K�Ĺ����r�������

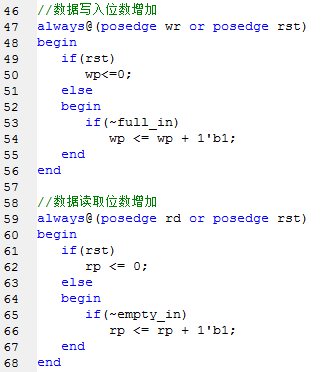

1.4.3 ����ݔ��ݔ��ģ�K

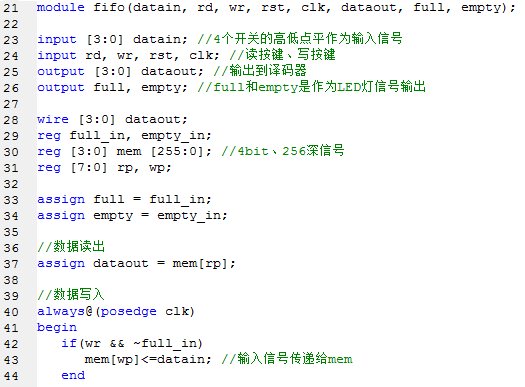

ͨ�^4���_�P���F4bit������ݔ�������������밴�I���r��������������ҼĴ���ָ�ָ����һλ�����xȡ���I���r����x������ݔ���һ��������������������xȡ�r�g���ɡ�

1.4.4 �g�aģ�K

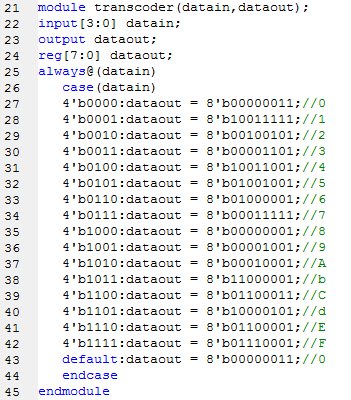

��4λݔ���BCD�a��4���g��8λ���M�ƴ��a���ڔ��a���@ʾ������

�����Y���cӑՓ

2.1 �{ԇ���E�c�F��

2.1.1 �{ԇ����

�������ͨ�^�Д�������̖�c�xȡ��̖�ĸߵ��ƽ�����Ɣ�����ݔ���cݔ����������r���̖��������ֱ�ӿ���ָ�+1����o�������S�r��ݔ���cݔ�����Ҍ�����ݔ�뷽ʽҪ��O�ߣ��G���ʸߡ�

֮���ij���ͨ�^�Д�������̖�c�xȡ��̖�����������Ɣ�����ݔ���cݔ����������ͬ�r����ָ�+1�����yԇ���������S�r��ݔ���cݔ����Ŀǰ�G���ʞ��㡣

2.1.2 ����

��ʼ�������ڷ��������ݔ��18λ������������̖���ָ��ƽ�r������һ���ٶ�ݔ���������xȡ��̖���ָ��ƽ�r����������������x�����

���M�������ڷ�������ЇLԇݔ��ɂ������������x����������yԇ�����������

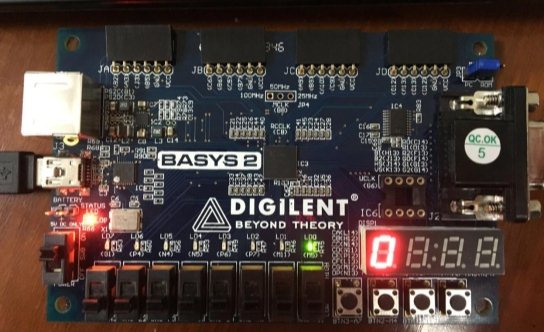

2.1.3 ��������Basys2�_�l��

��ʼ�����o�������x��������M�����yԇ��������

2.2 ���F���}�c����

���}һ������r�����x������������������M�_�l��r�yԇ�����������

����������r�r�g�O�ò������O�Þ�ÿ100���r�g��λݔ��һ�����������Ǵ˕r100KHz�ĕr���̖߀δ���F�^һ�������أ����Ԕ����o������������

���}��������r�ܟo�ތ��딵�������ֻ���xȡ���һ�������������

������ÿ�Δ�������rָᘛ]��ָ����һλ����������ݔ���һֱ���w֮ǰ�Ĕ�����������ԕr�ֻ���xȡ���һ�����������

���}����������16����������ֻ�ܴ惦15��������

�����������ĵ�0λ�Ĵ����_ʼ���攵�����������ڌ�����̖ͬ�r�����������Č����cָᘵ�ָ��������������_��15λ�r����ָᘲ�����ָ����һλ������Ҳ�Ͳ����܌��룬�������Ĵ���0-14λ�Ĵ��������

2.3 �����P�����ķ����cӑՓ

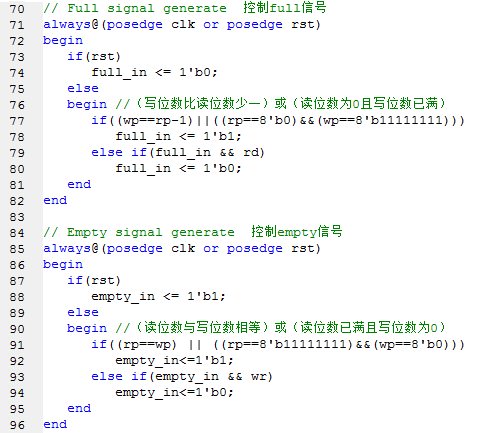

FIFO�Ďׂ���Ҫ������

1�����ȣ����ȼ�4bit��ÿ����������λ�����ԓ�����п������Č������

2�������ȣ����ָ�܉�Ĕ��������������ԓ�����п�����������������Uչ����

3�����M��־���M��־������ֹ�����������ɵ�������Д�FIFO�Ƿ��ѝMʮ����Ҫ����

4��������־����־������ֹ�����xȡ����ɵğoЧ�����x����

5����������ָᘣ�ָ����һ��Ҫ����ĵ�ַ��������rͬ�r��1��

6��������xȡָᘣ�ָ����һ��Ҫ�xȡ�ĵ�ַ������xȡ�rͬ�r��1���

�����ĵ��w��

3.1 �OӋ���c

���n���OӋ�\��Verilog HDLӲ�������Z�����ͨ�^Xilinx��˾��ISEܛ���M�г����Լ�����������������������Basys2�_�l�壬�OӋ���F��һ�N4bit-256���ͬ��FIFO�������ṩ�������_���������ͬ��֮ǰӲ���·�n���OӋ��C�Z���n���OӋ�����n���OӋ��Ҫ�Y��Ӳ����ܛ��֪�R�����Ҫ����Verilog HDLӲ�������Z��������ϤBasys2�_�l���Ӳ���·�����ϸ�ģ�K��ʹ�÷�����

�OӋ��ͬ��FIFO���Ȟ�4bit�������Ȟ�256�����������ڳ��������������Uչ�������ͨ�^4λ�_�Pݔ�딵�������밴�I�_�Jݔ��Ĕ�������xȡ���I�xȡһ�l�����������@���OӋ�����ք�ݔ�딵��������M��־LED����ʾ����ѝM������־LED����ʾ����ǿՠ�B���������^�졣ʹ�Ô��a���@ʾ4λ2�M�Ɣ��������������ð���ģ�K�YԴ��������������OӋ���

3.2 �u���Y��

����Basys2�_�l��������F��FIFO�������Ҫ����ͨ�^�ք�ݔ�딵��ģ�M��ͬ�����l��ģ�K�gͨ�ţ�߀���܌��H�\�������

���Ҵ��ڳ�����16���ֻ�ܴ惦15�������Ć��}��ԭ���ǔ����ĵ�0λ�Ĵ����_ʼ���攵������������ڌ�����̖ͬ�r�����������Č����cָᘵ�ָ��������������_��15λ�r���ָᘲ�����ָ����һλ������Ҳ�Ͳ����܌��룬�������Ĵ���0-14λ�Ĵ����������

3.3 ���ƽ��h

(1)ͨ�^����I�Pݔ�딵���Ϳ���ݔ����x�����������

(2)ʹ��Һ����Ļ�@ʾ��������־�M���ՠ�B����������������棻

(3)�����ք�ݔ��λ������ȅ�����

3.4 �����w��

ͨ�^�����n���OӋ������҂�얹̺ͼ����ˡ�VerilogHDL�����OӋ�c�C�ϡ��c��������Ӽ��g�����T�n�̵���Փ֪�R�����ã��J�R���˻��A֪�R��һ�Ќ��`�Ļ��A��ֻ�����պ�����Փ֪�R��������ܸ��õ�ʹ�ù���ȥ���OӋ�c���¡�

������ڼ��ό����a��ʹ��ܛ���������a�������Լ��r������CЧ���������ͨ�^���`�������W֪�R����Ϥʹ��VerilogHDL�Z���M���·�OӋ�IJ��E�c��������W��ISEܛ�������Լ���������������֮��ܛ������һ������Ĺ��ߣ����҂��OӋ�����s���Ŀ������������ڌ��Hʹ��Basys2�_�l�������������оƬ�Еr�����F�˸��N���}������҂�ͨ�^��醾W�j�Y�ϡ�ԃ���ώ���ͬ�W�����ȶ�N��ʽ�������}һһ��Q���ڽ�Q���}���^�����҂������ˌ�ܛ����ʹ�ú͌�֪�R�c�ČW������

�҂��J�R�������`����������δ������S�����}�������ҳ����}ԭ�����Q呟����҂�����Y�������������˼�����������S�����҂��Č��`��ʹ�҂�������·�OӋ���Mһ�����J�R�������҂����ڌ��OӋ�c�����ČW���춨�˻��A���

�塢�����īI

1��Szwagrzyk J, Whitt J K. FIFO peek access: US, US7773453[P]. 2010.

2����Ԭ���s, ���f��, �Z�Ƶ�,��. ��Verilog HDL�M��FPGA�OӋ��һЩ��������[J]. Ӌ��C��Ϣ���y�x���Ԅӻ�, 2004, 20(6):93-94.

3.���� ���� ���IJ�. XILINX ISE DESIGN SUITE 10��X FPGA�_�lָ��(߉�OӋƪ)[M]. �����]�, 2008.

4.ꐰ��r. С�����M�ƴa��BCD�a���D�Q[J]. ��Ӽ��g����, 1982(6).

����������

���һRTLԭ��D

��䛶���Ʒ�DƬ

�D 1 ��ʼ��B�������FIFO�О��

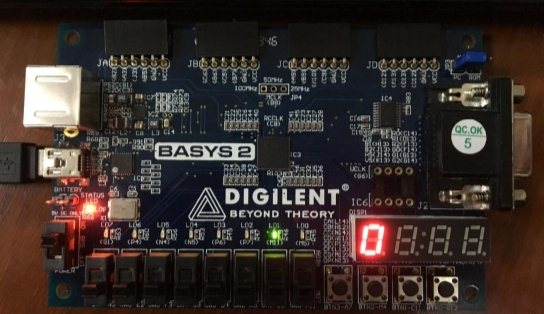

�D 2 �O�ú�ݔ�딵�����������I

�D 3 ���딵����;�xȡ����

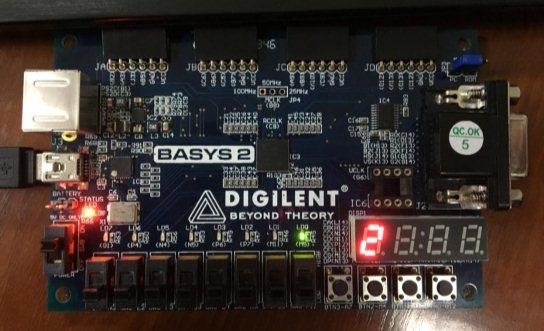

�D 4 ���딵���ꮅ�������M��̖����

�D 5 �xȡ�����ꮅ�����������̖����

������Word��ʽ�ęn51�����d��ַ���Ⱥ������DƬ����

Verilog�n�O���.docx

(916.49 KB, ���d��: 28)

Verilog�n�O���.docx

(916.49 KB, ���d��: 28)

2018-4-2 13:08 �ς�

�c���ļ������d����

���d�e��: �ڎ� -5

| �gӭ���R (http://www.raoushi.com/bbs/) |

Powered by Discuz! X3.1 |

Verilog�n�O���.docx

(916.49 KB, ���d��: 28)

Verilog�n�O���.docx

(916.49 KB, ���d��: 28)